- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I am using Cyclone 10 GX for an embedded project with Nios 2.

Quartus Pro 19.2 + C 10 GX + MT25QU256

For unknown reason, the Nios 2 did not boot.

I have to manually download the elf again through JTAG..

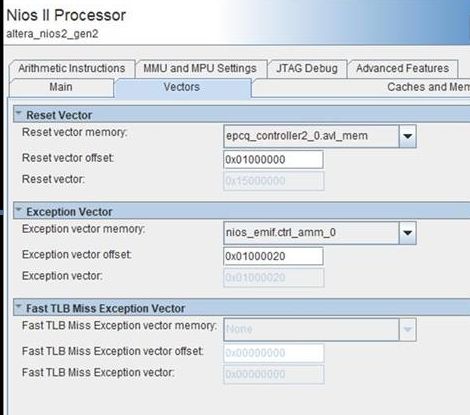

Setting in Qsys,

Linker,

Memory map,

BRs,

Johnson

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Johnson

Can we close this ? you may open a new one if you still have inquiry and want to follow up.

Thanks.

Eric

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Johnson

Can you check if the reset vector offset is larger than the FPGA image size ?

For instance, if the size of the FPGA image is estimated to be less than 0x01E00000, you can set the Nios II Reset Vector offset to 0x01E00000 in Qsys, which is also the start of the boot copier.

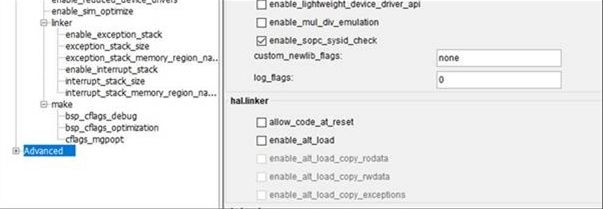

Also make sure that All settings in Settings.Advanced.hal.linker in BSP editor are left unchecked.

Thanks.

Eric

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Eric,

Thank you for getting back,

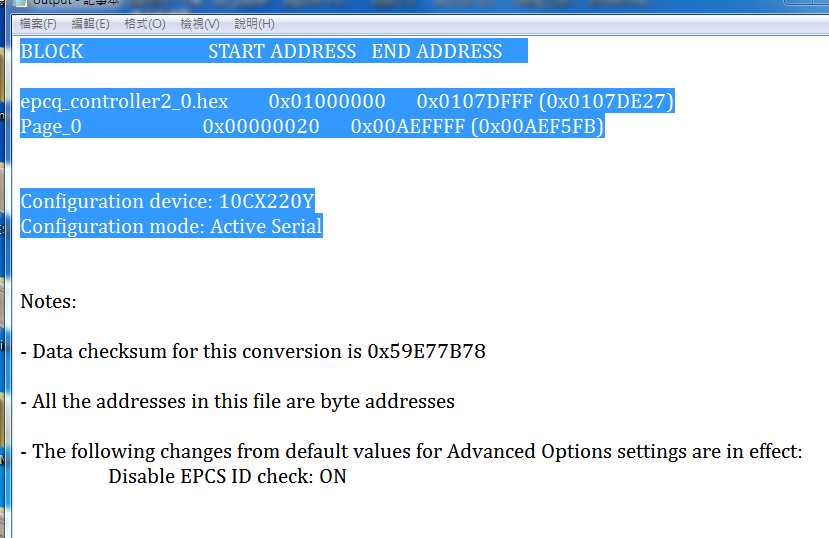

From my post above at the last image, FPGA will use flash up to 0x00AEFFFF.

And Nios starts from 0x010000 to 0x0107DFFFF.

And Link setting in BSP editor are left unchecked as above..

Would it be possible caused by the elf to hex conversion?

As in Q19.2, the tool has problem that I have to do it manually.

And I am not sure this tool will cover Micro Flash or not..

BRs,

Johnson

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Johnson

Do you mean you could program MT25QU256 flash according to the address range above using JTAG and Nios is booting ?

Thanks.

Eric

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Eric,

I can program the flash using JTAG + SFL or AS mode.

FPGA and Nios CPU is up but not the application.

I have to download the elf again through JTAG..

FYI!

BRs,

Johnson

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

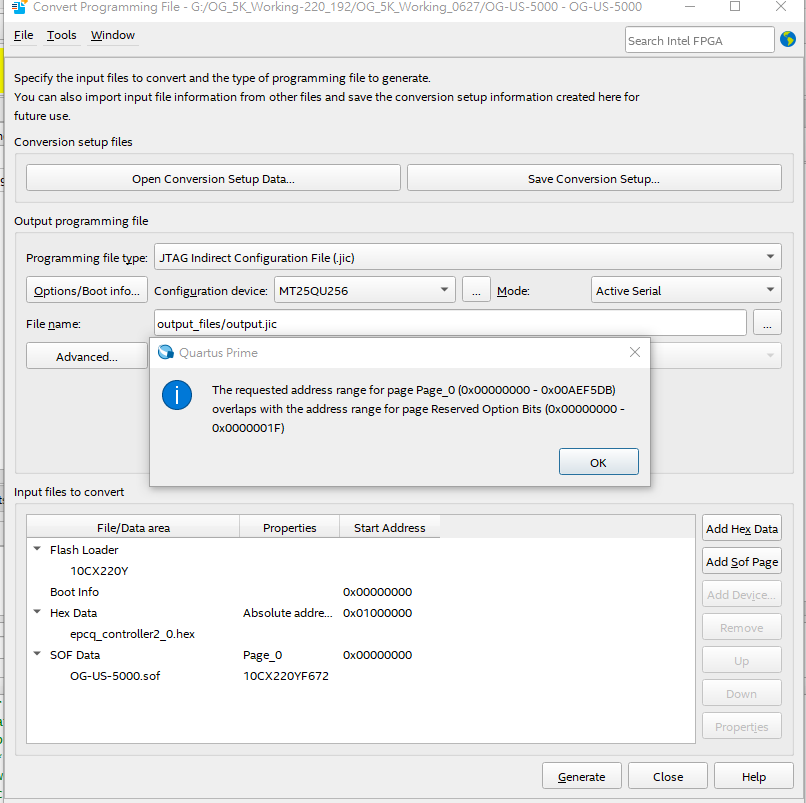

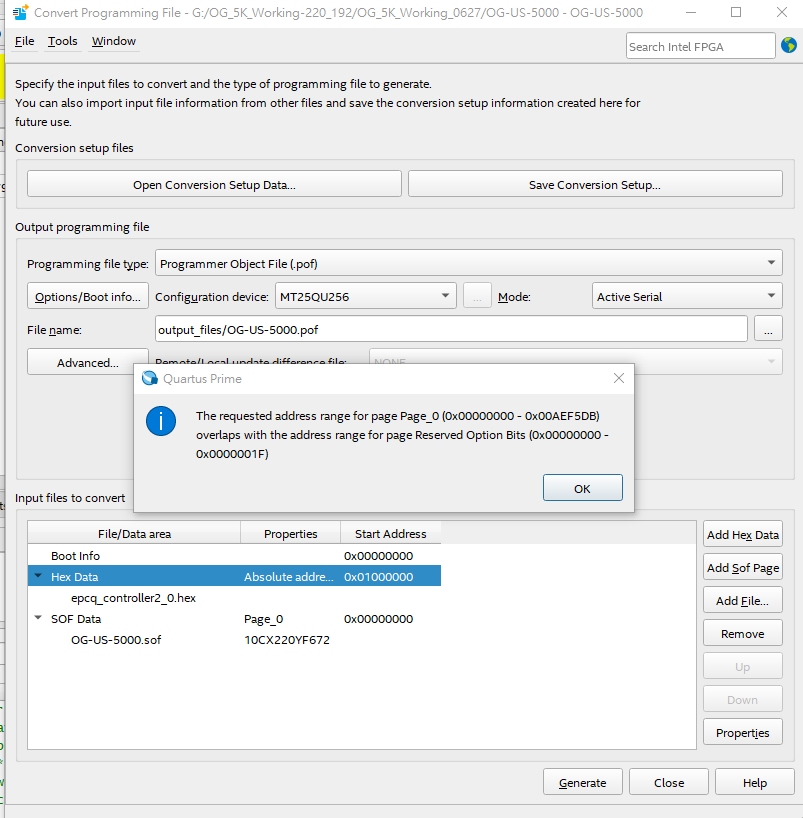

Hi Eric,

I

followed your instructions to generate the jic and pof by assign the start ti

0x00 instead of "auto".

Then

the converting can not execute because of errors.

I attach the images for your reference.

jic_gen

pof_gen

BRs,

Johnson

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Johnson

Then you may use auto or 0x00000020 as start address.

For the .hex generation, may I know what problem you face when you generate .hex from .elf in Quartus 19.2 ?

At the meantime, I will look at the manual method you use to convert .elf to .hex and will get back to you.

Thanks.

Eric

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

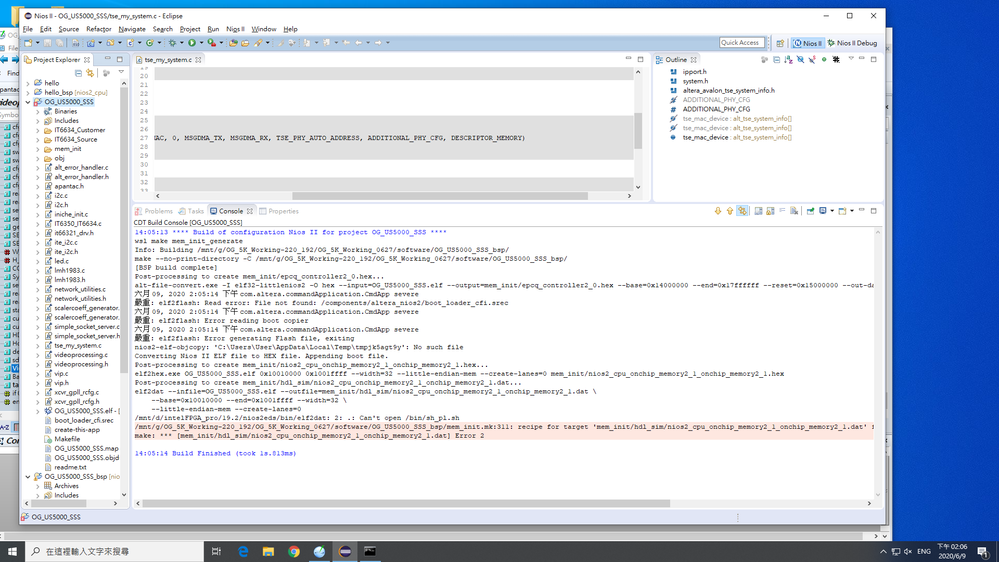

Hi Eric,

Thanks!

Use the 0x0000_0020 offset value worked and jic file generated without problem.

But the program was not running after programming.

The error message while executing mem_init_gen, please see below.

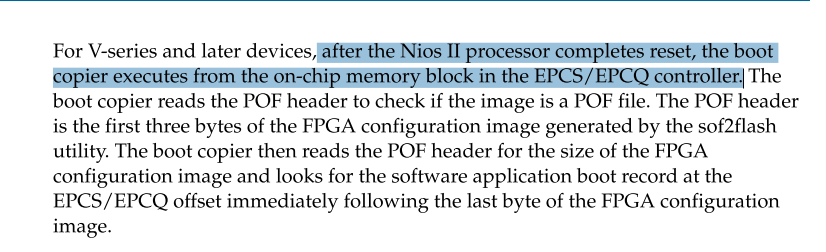

By the way, I am study AN458 about boot copier.

It mentioned boot copier executes from the on-chip memory block in EPCQ controller..

How do I know it is working?

BRs,

Johnson

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Eric,

One quick question,

May I use Generic Serial Flash to replace EPCQ for Nios 2 ?

I instantiate it in platform designer and assign reset vector to it.

But BSP editor does not show it in Linker Section.

BRs,

Johnson

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Johnson

Please also remember to compress your .sof under Properties when Convert Programming File, to .jic.

If still failed, can you send to me your design files ?

Thanks.

Eric

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Eric,

I don't think the compression will work as it only worked for sof file.

And my FPGA image is always fine..

I will test it and reply you later.

What design file do you need, sof + elf ?

BRs,

Johnson

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

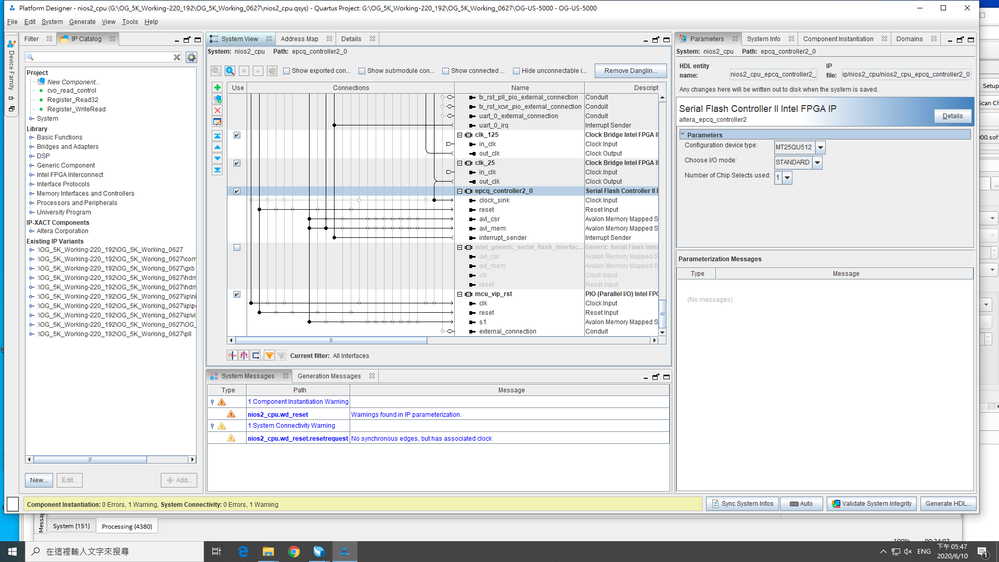

Hi, Johnson

May I know which serial flash controller IP you used in your design ?

Thanks.

Eric

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Eric,

I am using EPCQ2 controller.

FYI!

BRs,

Johnson

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Johnson

Would you try this, when you generate the .hex from .elf using mem_init_generate utility in your EDS, ie right click on project in Project Explorer, and Make Targets > Build.

After you get your .hex under mem_init folder, also look for meminit.qip, and add this meminit.qip to your Quartus project and then generate the .sof.

Next when you convert the programming file, just convert this .sof to .jic or .pof, and then program this .jic or .pof into your flash.

Thanks.

Eric

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Eric,

I checked my current Quartus project and the meminit_qip was included already.

The steps you mentioned is not work because,

1. EDS did not allow the generation of hex to elf. The tool is not work as mentioned before and in intel KDB.

2. When I tried the mem_init, the old elf will be deleted and no file will be generated.

3. Include the mem_init.qip will only work when nios execute in on-chip memory.

BRs,

Johnson

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Johnson

My apologize for the delay.

Due to Khronos migration, I couldn't find your attachment here from your latest emails.

Would you mind to forward to me your attachment again on the flash test result and your findings ?

Thanks.

Eric

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Eric,

Please download the zip file and check the contents inside.

Shared folder include the jic file with both FPGA image and Nios 2 flash.

Qsys is the controller I am using now, Generic Quad SPI running at 25MHz.

I checked the clock frequency on board.

From the linker, Nios2 will run on DDR.

Then I use qspi flash controller to read and print the content in device at address 0x0100_0000.

Include check the device ID.

This is where the APP stored.

JIC is the shared jic file that I use reader to get the raw data.

You can compare it with nios2_shell_print, they are of the same.

Therefore I am confirm the programming to flash and the content inside should be fine.

Unfortunately, the program is not running and I have to download the elf to make it work.

The problem is bootcopier or the converted file?

BRs,

Johnson

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Eric,

Good day!

Do you have any update on the issue after receiving my shared files?

Please let me know.

Thank you!

BRs,

Johnson

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Johnson

Can you try to run timing analysis and check if you have no timing violation ?

You may constraint the Nios core, GQSPI controller II and other IPs which are timing critical.

Thanks.

Eric

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Johnson

Can you refer to page 24 of below document on how to debug your boot copier ?https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/an/an458.pdf

Thanks.

Eric

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Johnson

Have you tried to debug the boot copier according to the document I provided ?

Thanks.

Eric

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page