- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi support,

I am learning the simple socket server design on Cyclone 10 GX.

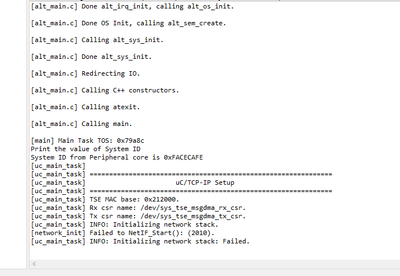

For unknown reason, the initialization process stopped with the error code (2010),

It's the TSE with DP83848.

The signals on MDIO and MDC is working.

Therefore I would like to know how to debug this issue.

Thank you.

BRs,

Johnson

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

Did you managed to run the example design on the Cyclone10 EVB yet?

Please note the following setting when trying to generate the BSP for the application.

5.5.2.2. Configuring the BSP (intel.com)

For the application you could reuse the application code from the latest design example.

Regards

Jingyang, Teh

Link Copied

- « Previous

-

- 1

- 2

- Next »

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

HI

I am Jingyang and I will be taking over the case from Eber.

Sorry for the late response as there are a surge in cases at the moment.

Please give me sometime to try get the example design running and try probe the behavior of the ff_rx_rdy pin.

Regards

Jingyang, Teh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

Sorry there is a current surge in case and I will need more time in this case.I managed to run the example design and able to connect to the board through Telnet. Currently I will need more time to acquire the signalTap waveform.

Previously when you switch the Example Design to DHCP. Are you able to connect to the board through Telnet?

Regards

Jingyang, Teh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jingyang,

Thank you for the update.

So you can run the example design on the Cyclone 10 GX device and can telnet it?

If this is the case, would you share me the example?

As I never have any change to connect to the board.

BRs,

Johnson

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

I tried it on an Arria10 board. I think it should be okay if we migrate it over to the Cyclone10.

Attached is my project for the Arria10.

Let me try to migrate it to the Cyclone10 board and share u the project again.

Regards

Jingyang, Teh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jingyang,

Thank you for the update.

I hope to receive the C10 project soon.

BRs,

Johnson

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jingyang,

Do you have any update on the C10 project?

Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

Sorry for being so slow.

I got a hard time getting your project to work .

I think in your project you did not assigned the pins correctly.

Still trying to migrate and testing out the example design.

attached is so far i managed to get the application running boot into initialization.

Still solving the error code 20014 that i am looking at.

Regards

Jingyang, Teh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jingyang,

I just saw the update.

After download the qar but I can't open it at Quartus Pro 23.2..

By the way, what's the error code 20014 you mentioned?

It's in my previous shared package?

BRs,

Johnson

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Johnson

Could you try with the latest 23.4 Quartus?

I have migrated the latest NiosV example design to the cyclone10 gx board.

I managed to solved the error code 20014.

Now i am stuck with the same error code that you are facing. 2010

Right now i am asking around what could be the cause for this.

Regards

Jingyang, Teh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

I managed to get pass the error. It seems that in the previous design I did not connect the reset for the ethernet phy.

Please find the latest project with the correct pin placement.

You would need to assign these pin in the pin planner.

Screenshot of the results

Regards

Jingyang, Teh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jungyang,

Thank you for the update.

Let me check on the C10 EVB and get back to you my finding later.

BRs,

Johnson

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

Did you managed to run the example design on the Cyclone10 EVB yet?

Please note the following setting when trying to generate the BSP for the application.

5.5.2.2. Configuring the BSP (intel.com)

For the application you could reuse the application code from the latest design example.

Regards

Jingyang, Teh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jingyang,

Thank you for the link..

I can see the example running now.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

I’m glad that your question has been addressed, I now transition this thread to community support. If you have a new question, Please login to ‘https://supporttickets.intel.com/s/?language=en_US’, view details of the desire request, and post a feed/response within the next 15 days to allow me to continue to support you. After 15 days, this thread will be transitioned to community support. The community users will be able to help you on your follow-up questions.

Regards

Jingyang, Teh

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page

- « Previous

-

- 1

- 2

- Next »