Hi,

I'm trying to get the Hello World Nios II example to run on an Cyclone 10 GX. The design build and the sof-programming run without a problem. But the Nios II Eclipse can't find the Nios as target connection.

In the "Run Configuration" dialog it shows:

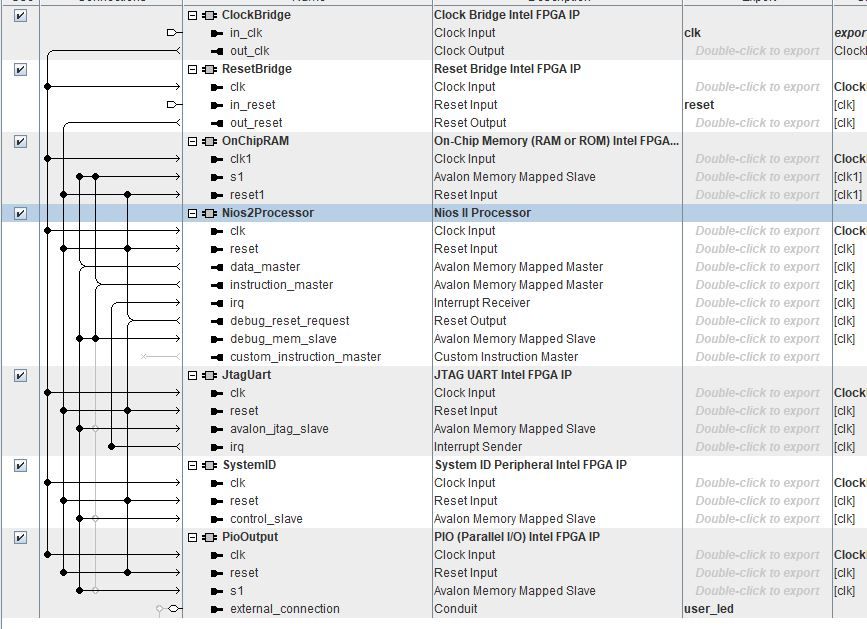

No Nios II target connection paths were located. Check connections and that a Nios II .sof is downloaded.The Nios II system is pretty basic:

with the following settings:

- Clk Input is 100 MHz (50 Mhz doesn't work neither)

- Reset Input is active high

- Nios II:

- Nios II/e

- Reset/Exception vector memory: OnChipRAM.s1

- Include JTAG Debug

- The rest is unchanged

- OnChipRAM:

- Type: RAM

- Block type: Auto

- Size: 200000 bytes

- The rest is unchanged

- The other components (JtagUart / SystemID / PioOutput) have the default settings

And I've checked, that the Nios Core is part of the design (using the Technology Map Viewer of the final snapshot).

Can you please give me a hint what I'm doing wrong?

Thanks

链接已复制

Hi,

Before "run as hardware" you should configure the fpga with the .sof file generated

If you get a popup saying "no Nios II target connection paths were located", go under the Target connection tab, click refresh connections.

Have you download the correct .sof ?

Have you selected correct sopcinfo file while creating the eclipse project?

Check pin assignments of clk and reset?

Regards

Anand

Hi,

Yes, the correct .sof file is downloaded to the FPGA and runs.

Yes, it is the correct sopcinfo file.

Clk (100Mhz) and Reset (high active) are correctly connected and are working.

The Target connection tab shows no target even after multiple refreshes.

I've set the following clock constraints:

create_clock -name {CLK_100MHz} -period 10.000 -waveform { 0.000 5.000 } [get_ports {CLK_100MHz}]

derive_pll_clocks

create_clock -period "30.303 ns" -name {altera_reserved_tck} {altera_reserved_tck}The altera_reserved_tck constraint is based on this Knowledge Base article.

Hi,

That doesn't work neither.

But I had it shown up for once as a target connection (without changing anything) this morning, and after that the problem came back ...

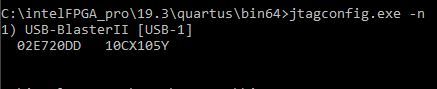

Based on this documentation, a jtagconfig -n should output something like

$ jtagconfig -n

1)

Intel® FPGA Download Cable [USB-0]

020050DD EP1S40/_HARDCOPY_FPGA_PROTOTYPE

Node 11104600

Node 0C006E00But mine outputs no nodes:

could this be the reason? And how to solve this?

Hi,

I'm having the same issue with my Cyclone 10 FPGA on Ubuntu 20.04 and tried everything @AnandRaj_S_Intel suggested. I also tried running the nios2_command_shell script and then ran 'nios2-terminal', which couldn't run due to the lack of detected devices. But when I run jtagconfig, I can see my blaster connected and also the Cyclone under it, just like the snippet above.

Cheers

Hi anonimcs,

Can you share the error log output when you run nios2-terminal command? I suspect the Nios II processor isn’t present in the loaded .sof, or its debug interface isn’t correctly configured.

Thanks,

Alif

Hi Michael,

Regarding Jtagconfig -n.

- Your image does not contain a Nios II processor with a JTAG debug module enabled or JTAG UART component.

- Load image with Nios II processor with a JTAG debug module enabled

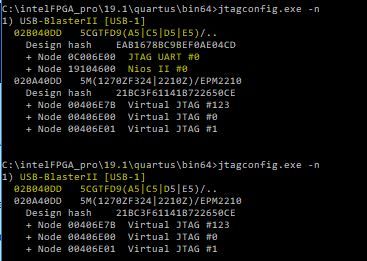

For example, check the image

Are you using a cyclone 10 GX dev kit? IF yes please try to load the factory image.

Regards

Anand