- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi.

From the Programmer Utility you can create an advanced .jbc file from a .pof file. (E.g. program configuration and user flash partitions in Max10)

If you enable .jbc file generation through the Device&Pin Options => Programming Files settings, the .jbc file is generated from the .sof file only and only capable of configuring a Max10.

Is there a way to make an advanced .jbc file as part of the normal compilation flow?

Best regards

Nikolay

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Nikolay,

You can create .jbc file using Quartus Programmer.

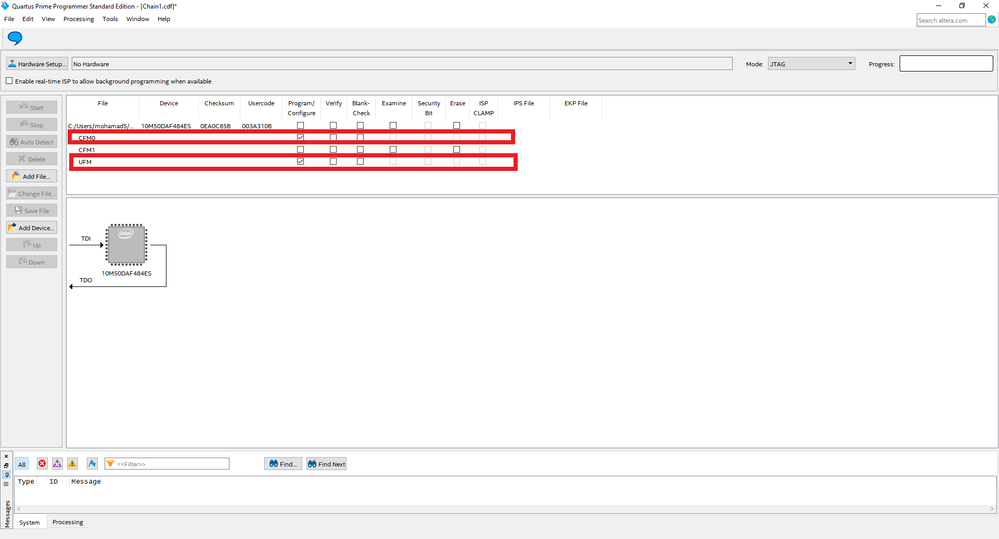

Add your .pof file. Choose which CFM/UFM you want to program. (My case I choose CFM0 and UFM)

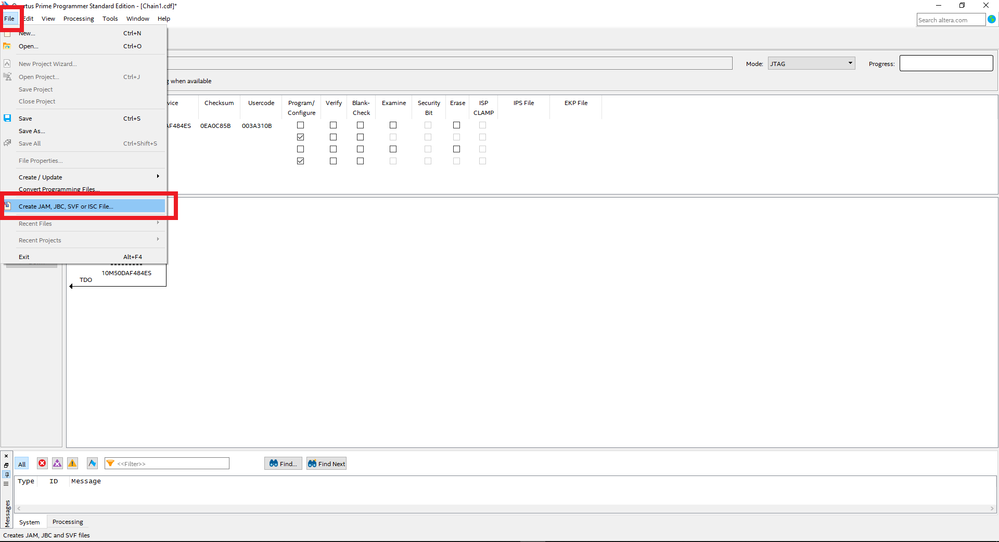

Then, go to file --> Create JAM, JBC, SVF and ISC file.

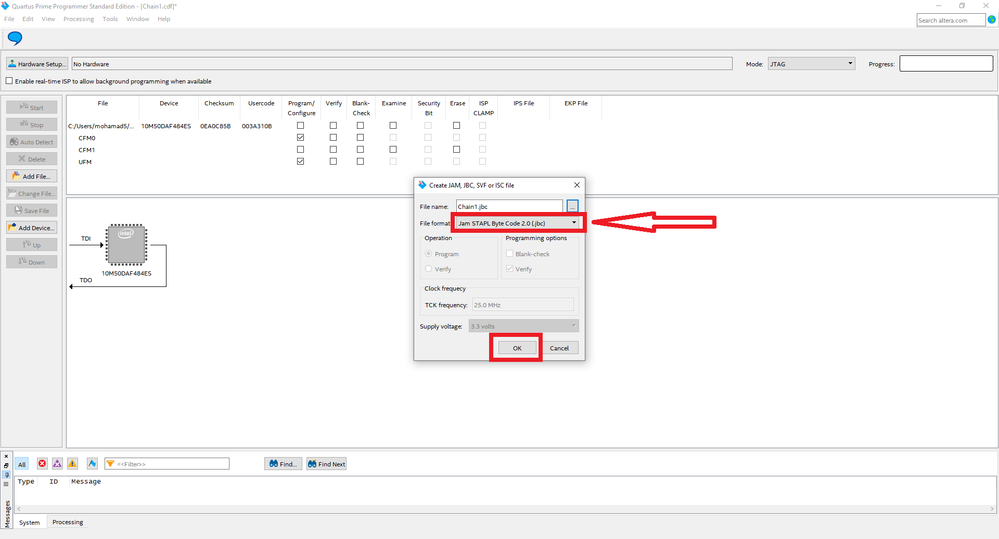

Then, choose .jbc file.

I hope this will help.

Cheers.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

This is not what Nikolay asked about. He already stated that he knows how to do it using the programmer..

The question was

"Is there a way to make an advanced .jbc file as part of the normal compilation flow?"

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Shafiq.

There is a project assignment that can potentially be used in this case: POST_FLOW_SCRIPT_FILE

The next question is therefore:

What is the tcl/shell command to make the advanced .jbc file as you described above?

Regards

Nikolay

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Nikolay,

You can use quartus_cpf command to convert input file (.sof or .pof or .cdf file) to .jbc file.

Here the example the command:

- quartus_cpf -c <input_sof_file> <output_jbc_file>

- quartus_cpf -c <input_pof_file> <output_jbc_file>

- quartus_cpf -c <input_cdf_file> <output_jbc_file>

I hope this will help.

Cheers

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Shafiq

I have tried that and that, both with pof and cdf and it dosn't work. It is as if some option are missing. The messages from the JAM pplayer is also different from when the jbc file is generated be the programmer. The programmer makes more of those DO_*********** (optional)

jbc generated by quartus_cpf

CRC matched: CRC value = 0000FC76h

File format is Jam STAPL ByteCode format

NOTE "CREATOR" = "QUARTUS PRIME JAM COMPOSER 18.1"

NOTE "DATE" = "2020/03/05"

NOTE "DEVICE" = "10M02SC"

NOTE "NEED_FREQUENCY_CONTROL" = "0"

NOTE "FILE" = "ctx_mbf7332D201_ic1.pof"

NOTE "TARGET" = "1"

NOTE "IDCODE" = "031810DD"

NOTE "USERCODE" = "000BAF3E"

NOTE "CHECKSUM" = "006DC5C8"

NOTE "SAVE_DATA" = "DEVICE_DATA"

NOTE "SAVE_DATA_VARIABLES" = "V0, A12, A13, A25, A42, A93, A43, A92, A94, A95, A105, A109, A111"

NOTE "STAPL_VERSION" = "JESD71"

NOTE "JAM_VERSION" = "2.0"

NOTE "ALG_VERSION" = "68"

Actions available in this file:

PROGRAM

DO_BLANK_CHECK (optional)

DO_VERIFY (recommended)

DO_BYPASS_CFM (optional)

DO_BYPASS_UFM (optional)

DO_BYPASS_ICB (optional)

DO_BYPASS_CFM1 (optional)

DO_READ_USERCODE (optional)

BLANKCHECK

DO_BYPASS_CFM (optional)

DO_BYPASS_UFM (optional)

DO_BYPASS_ICB (optional)

DO_BYPASS_CFM1 (optional)

VERIFY

DO_BYPASS_CFM (optional)

DO_BYPASS_UFM (optional)

DO_BYPASS_ICB (optional)

DO_BYPASS_CFM1 (optional)

DO_READ_USERCODE (optional)

CONFIGURE

DO_READ_USERCODE (optional)

DO_HALT_ON_CHIP_CC (optional)

DO_IGNORE_IDCODE_ERRORS (optional)

DO_IGNORE_INTOSC_BYPASS (recommended)

DO_BYPASS_SECOND_IDCODE_READ (optional)

ERASE

DO_BLANK_CHECK (optional)

DO_BYPASS_CFM (optional)

DO_BYPASS_UFM (optional)

DO_BYPASS_ICB (optional)

DO_BYPASS_CFM1 (optional)

READ_USERCODE

CHECK_IDCODE

Device #1 IDCODE is 031810DD

configuring SRAM device(s)...

Device programming failure

Device configuration failure

jbc generated by programmer

CRC matched: CRC value = 00003C83h

File format is Jam STAPL ByteCode format

NOTE "CREATOR" = "QUARTUS PRIME JAM COMPOSER 16.1"

NOTE "DATE" = "2020/02/25"

NOTE "DEVICE" = "10M02SC"

NOTE "NEED_FREQUENCY_CONTROL" = "0"

NOTE "FILE" = "ctx_mbf7332D201_ic1_version_2.pof"

NOTE "TARGET" = "1"

NOTE "IDCODE" = "031810DD"

NOTE "USERCODE" = "000FA60E"

NOTE "CHECKSUM" = "00702D4F"

NOTE "SAVE_DATA" = "DEVICE_DATA"

NOTE "SAVE_DATA_VARIABLES" = "V0, A12, A13, A25, A43, A92, A94, A95, A105, A109, A111"

NOTE "STAPL_VERSION" = "JESD71"

NOTE "JAM_VERSION" = "2.0"

NOTE "ALG_VERSION" = "67"

Actions available in this file:

PROGRAM

DO_BLANK_CHECK (optional)

DO_VERIFY (recommended)

DO_DISABLE_ISP_CLAMP (optional)

DO_BYPASS_CFM (optional)

DO_BYPASS_UFM (optional)

DO_REAL_TIME_ISP (optional)

DO_FORCE_SRAM_DOWNLOAD (optional)

DO_BYPASS_ICB (optional)

DO_BYPASS_CFM1 (optional)

DO_READ_USERCODE (optional)

DO_INIT_CONFIGURATION (optional)

BLANKCHECK

DO_DISABLE_ISP_CLAMP (optional)

DO_BYPASS_CFM (optional)

DO_BYPASS_UFM (optional)

DO_REAL_TIME_ISP (optional)

DO_FORCE_SRAM_DOWNLOAD (optional)

DO_BYPASS_ICB (optional)

DO_BYPASS_CFM1 (optional)

VERIFY

DO_DISABLE_ISP_CLAMP (optional)

DO_BYPASS_CFM (optional)

DO_BYPASS_UFM (optional)

DO_REAL_TIME_ISP (optional)

DO_FORCE_SRAM_DOWNLOAD (optional)

DO_BYPASS_ICB (optional)

DO_BYPASS_CFM1 (optional)

DO_READ_USERCODE (optional)

ERASE

DO_BLANK_CHECK (optional)

DO_DISABLE_ISP_CLAMP (optional)

DO_BYPASS_CFM (optional)

DO_BYPASS_UFM (optional)

DO_REAL_TIME_ISP (optional)

DO_FORCE_SRAM_DOWNLOAD (optional)

DO_BYPASS_ICB (optional)

DO_BYPASS_CFM1 (optional)

READ_USERCODE

CHECK_IDCODE

Device #1 IDCODE is 031810DD

full-chip erasing Max 10 FPGA device(s) ...

programming Max 10 FPGA CFM0 block at sector 5 ...

programming Max 10 FPGA UFM block at sector 1 ...

programming Max 10 FPGA UFM block at sector 2 ...

verifying Max 10 FPGA CFM0 block at sector 5 ...

verifying Max 10 FPGA UFM block at sector 1 ...

verifying Max 10 FPGA UFM block at sector 2 ...

programming Max 10 FPGA DSM block ...

DONE

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi JChri1,

I send you a forum private message.

Please follow up there.

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi ShafiqY,

I'm dealing with this same matter when trying to generate a correct JAM file used for MAX10 internal FLASH update.

I managed to generate a working JAM file (using Qartus Programmer) after finding this knowledge base:

https://www.intel.com/content/www/us/en//support/support-resources/knowledge-base/component/2017/how-to-generate-a-jam-file-which-supports-the-option-of-dorealti1.html

That does not quite fit on my development flow as it does not rely on any GUI at all.

I need to find a way to ensure the property "DO_REAL_TIME_ISP" in the JAM files generated directly on "quartus_cpf" as it was possible with older Quartus versions.

Inspecting the Quartus configuration files trying to find how to let this property allways on I've found the "quartus2.qreg" file but unfortunately it does not affect the "quartus_cpf" behavior.

There is another configuration file or procedure available by command line to generate the JAM file with that particular property on?

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I've found the solution on MAX10 device's "Configuration User Guide".

On section "3.2.2. Generating Third-Party Programming Files using Intel QuartusPrime Programmer" is described the additional options available on quartus_cpf to generate the JAM file with the desired property "DO_REAL_TIME_ISP".

From the user guide:

"quartus_cpf -c <input_pof_file> <output_jam/jbc_file> -o background_programming=on"

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page