- Отметить как новое

- Закладка

- Подписаться

- Отключить

- Подписка на RSS-канал

- Выделить

- Печать

- Сообщить о недопустимом содержимом

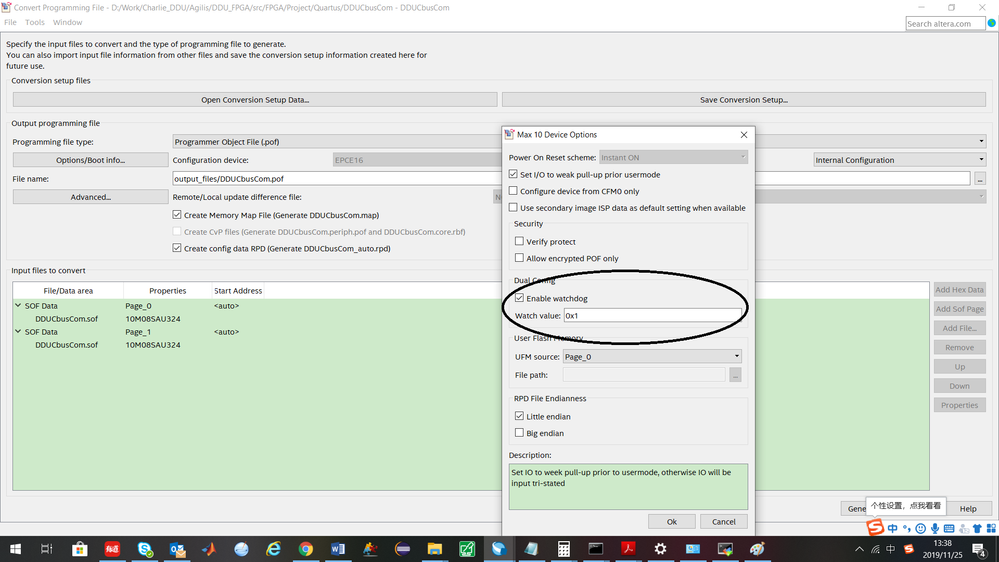

FPGA communicates with another FPGA with PHY chip. Normally(watchdog enable checkbox not checked), the PHY link led is always off when communication is good. While after I enble watchdog for dual-config(watchdog enable checkbox checked) and set watchdog value to any value, the link led will be on for about 2 seconds and return to be off. This will also be repeated after dozens of seconds. Why? How will I use the watchdog for dual-config? I didn't run remote update after power-up and the FPGA just run application firmware(just ethernet communication with another FPGA using PHY chip).

Attached file is my fpga code for the dual-config.

Ссылка скопирована

- « Предыдущий

- Следующий »

- Отметить как новое

- Закладка

- Подписаться

- Отключить

- Подписка на RSS-канал

- Выделить

- Печать

- Сообщить о недопустимом содержимом

Hi,

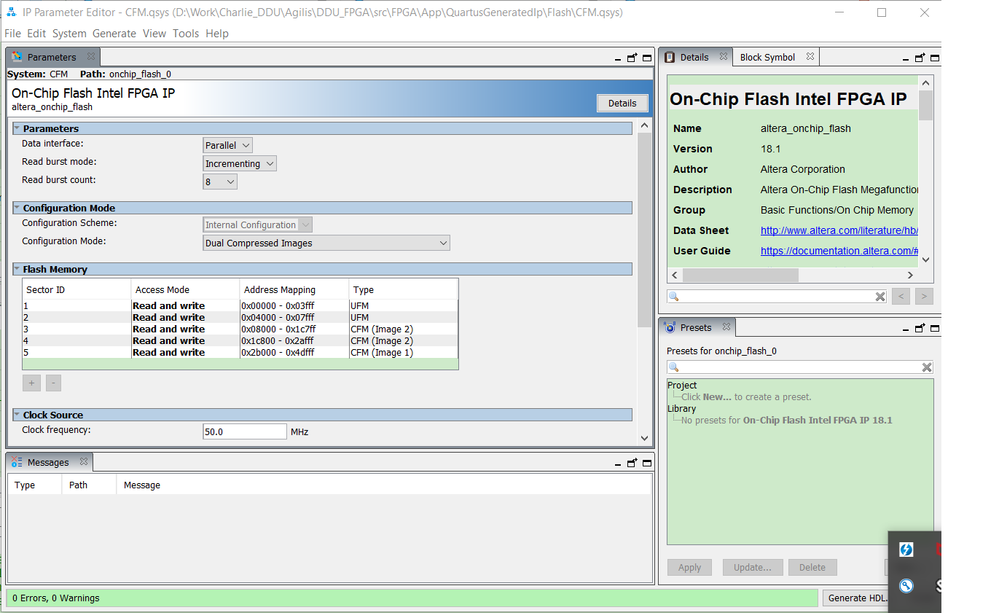

May I know if you have On Chip Flash IP in your design?

The design example that I provide is for your to create a sof file which can use it to update the UFM flash using rpd or writing directly to the exact location. Recompilation is not needed once you created the sof file for you to modify the UFM memory anytime.

- Отметить как новое

- Закладка

- Подписаться

- Отключить

- Подписка на RSS-канал

- Выделить

- Печать

- Сообщить о недопустимом содержимом

Hi,@JohnT (Intel)

Yes, I have On Chip Flash IP in my application design. Your proposal sounds good to me. Please tell me how to do. Thanks!

- Отметить как новое

- Закладка

- Подписаться

- Отключить

- Подписка на RSS-канал

- Выделить

- Печать

- Сообщить о недопустимом содержимом

Hi,

May I know how do you connect the On Chip Flash IP? Not sure if you are able to follow the connection in my attach design example on connecting the On Chip Flash IP to JTAG to Avalon Master? You may follow the guide in the document in order to run the System Console and update the UFM.

Please let me know if the document is not sufficient.

- Отметить как новое

- Закладка

- Подписаться

- Отключить

- Подписка на RSS-канал

- Выделить

- Печать

- Сообщить о недопустимом содержимом

Hi,@JohnT (Intel)

I just use flash IP and instantiated in VHDL. I just write and read with VHDL and didn't use others connected with flash IP. So please give me more specific resources about this. The userguide.dox is very simple and I can't get anythin about it.

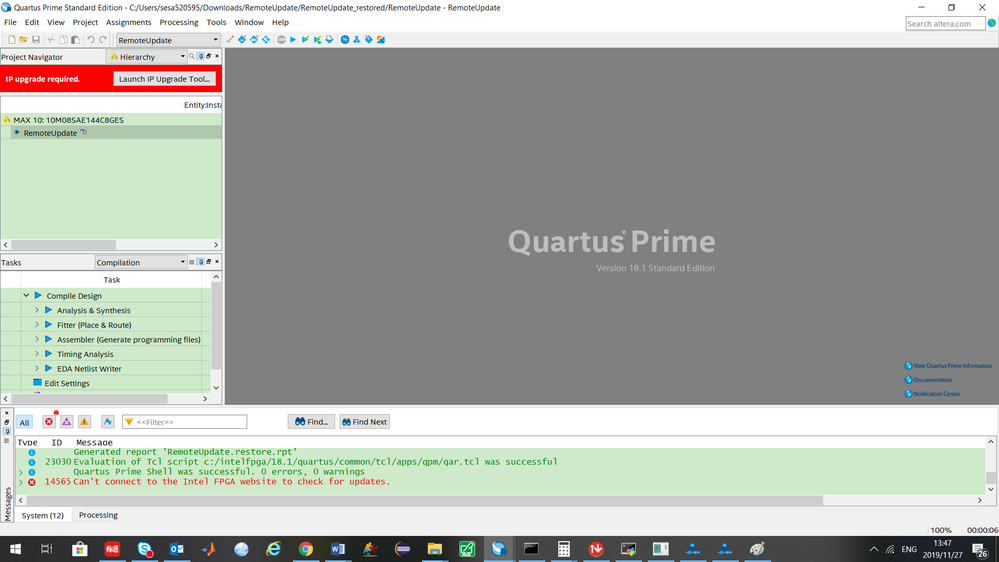

I also can just open the project you uploaded as pictures below, how to see the code ?

- Отметить как новое

- Закладка

- Подписаться

- Отключить

- Подписка на RSS-канал

- Выделить

- Печать

- Сообщить о недопустимом содержимом

Hi,

Please use Qsys or Platform Designer under Tools to open the system level design.

- Отметить как новое

- Закладка

- Подписаться

- Отключить

- Подписка на RSS-канал

- Выделить

- Печать

- Сообщить о недопустимом содержимом

I can only open file like this picture. But I can't see any other information like code to operate this qsys.

- Отметить как новое

- Закладка

- Подписаться

- Отключить

- Подписка на RSS-канал

- Выделить

- Печать

- Сообщить о недопустимом содержимом

Hi,

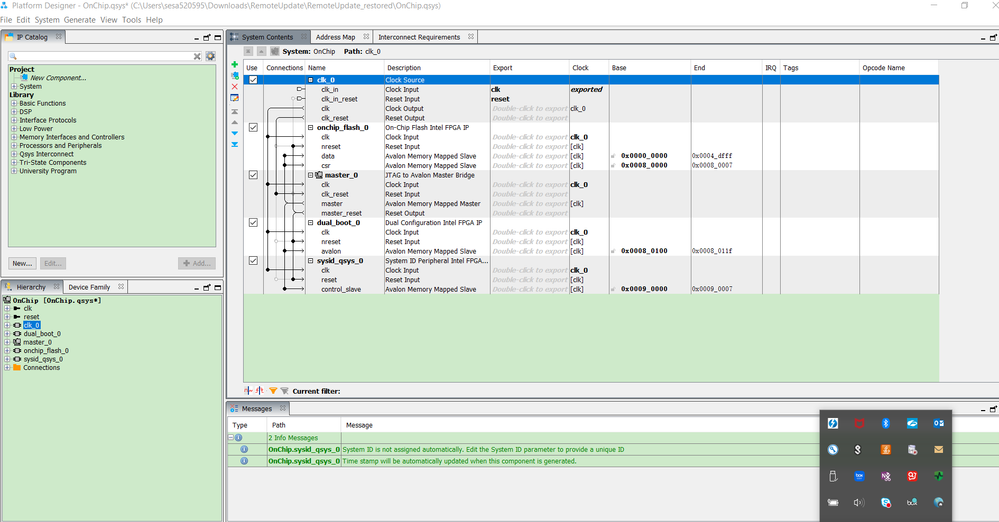

This is the connection. So when you generate the HDL code using Platform designer then it will generate the code for you.

The picture you are observing the overall connection where Platform Designer will show how the Avalon is connected.

- Отметить как новое

- Закладка

- Подписаться

- Отключить

- Подписка на RSS-канал

- Выделить

- Печать

- Сообщить о недопустимом содержимом

After connecting the On Chip Flash IP to JTAG to Avalon Master, then what's the next step? How to code in FPGA and how to operate to realize the function that I can modify the generated file and then directly program into FPGA.

Then FPGA will have application image in CFM and serial number in UFM.

- Отметить как новое

- Закладка

- Подписаться

- Отключить

- Подписка на RSS-канал

- Выделить

- Печать

- Сообщить о недопустимом содержимом

Hi,

After connecting and follow the memory mapping in the Platform designer, then you can directly use System Console to write it.

- Отметить как новое

- Закладка

- Подписаться

- Отключить

- Подписка на RSS-канал

- Выделить

- Печать

- Сообщить о недопустимом содержимом

Hi,@JohnT (Intel)

Thanks for your explanation. While I am a newer on this, so could you please tell me detaily on how to use System Console to write it?

- Отметить как новое

- Закладка

- Подписаться

- Отключить

- Подписка на RSS-канал

- Выделить

- Печать

- Сообщить о недопустимом содержимом

Hi,

Please open System Console and load the .tcl file provided. Then you can follow the userguide on how to use it. Just focus on using the ASMI parallel location as this is connected to On Chip Flash IP.

- Отметить как новое

- Закладка

- Подписаться

- Отключить

- Подписка на RSS-канал

- Выделить

- Печать

- Сообщить о недопустимом содержимом

Is System Console Quartus software? How to open it. I don't know what it is.

- Отметить как новое

- Закладка

- Подписаться

- Отключить

- Подписка на RSS-канал

- Выделить

- Печать

- Сообщить о недопустимом содержимом

Hi,

It is part of the Quartus software. In Quartus --> Tools --> System Debugging Tools --> System Console.

- Подписка на RSS-канал

- Отметить тему как новую

- Отметить тему как прочитанную

- Выполнить отслеживание данной Тема для текущего пользователя

- Закладка

- Подписаться

- Страница в формате печати

- « Предыдущий

- Следующий »