- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I am currently working Agilex FPGA (AGFB014R24B2E2V). For my design standalone GHRD I am able to program, but when I am adding the JESD example design to it, the following error is coming -

Error (18950): Device has stopped receiving configuration data

Error (18948): Error message received from device: Internal error. (Subcode 0x0001, Info 0x00000000, Location 0x00007C00)

Error (22248): Detected an error during configuration. Refer to the Configuration User guide for details on debug guidelines. Check the latest Intel Quartus Prime software release for possible fixes.

Error (209012): Operation failed

Info (209061): Ended Programmer operation at Tue Jan 24 14:20:17 2023

Error: Quartus Prime Programmer was unsuccessful. 4 errors, 0 warnings

Error: Peak virtual memory: 1945 megabytes

Error: Processing ended: Tue Jan 24 14:20:17 2023

Error: Elapsed time: 00:00:21

Error: System process ID: 22300

Kindly help me in the same regard. The .sof files I am able to generate but the programming is giving error.

Quartus version 22.2 and my VID settings are as follows -

set_global_assignment -name USE_PWRMGT_SCL SDM_IO0

set_global_assignment -name USE_PWRMGT_SDA SDM_IO12

set_global_assignment -name VID_OPERATION_MODE "PMBUS MASTER"

set_global_assignment -name PWRMGT_BUS_SPEED_MODE "400 KHZ"

set_global_assignment -name PWRMGT_SLAVE_DEVICE_TYPE OTHER

set_global_assignment -name PWRMGT_SLAVE_DEVICE0_ADDRESS 4F

set_global_assignment -name PWRMGT_PAGE_COMMAND_ENABLE ON

set_global_assignment -name PWRMGT_VOLTAGE_OUTPUT_FORMAT "LINEAR FORMAT"

set_global_assignment -name PWRMGT_LINEAR_FORMAT_N "-12"

Thank you

Shubhangi

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Shubhangi,

Thank you for reaching out.

Just to let you know that Intel has received your support request and currently we are confirming the details with our internal team.

Allow me some time to look into your issue. I shall come back to you with findings.

Thank you for your patience.

Best Regards,

ZulsyafiqH_Intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Shubhangi,

Thank you for your patience.

We could not replicate your error on our side and currently I am running some test to replicate it.

I believe there is a similar case ticket reported by you in below link:

Case - Not able to program Agilex FPGA

I would like to clarify with you is the case same issue? duplication of case?

If it is the same, I have provided you some input for you to try from your side.

However, I will paste the same answer here.

Thank you.

Best Regards,

ZulsyafiqH_Intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Shubhangi,

Good day.

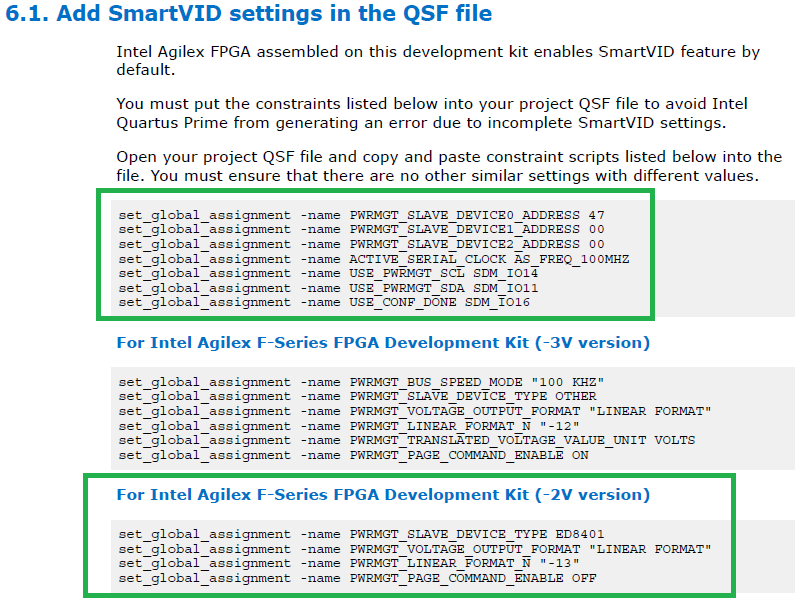

After further checking it seems like it might be some issue with the VID settings.

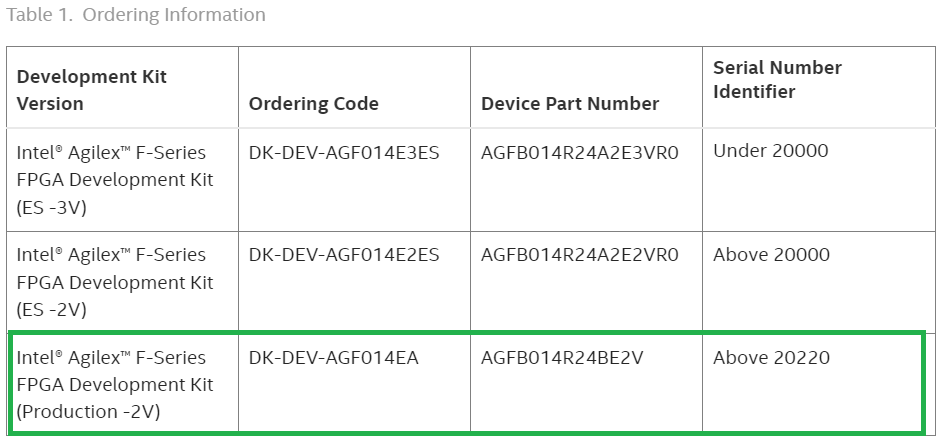

Based on your Agilex part number, I believe you are using the Agilex F-Series FPGA devkit Production-2V.

For the VID setting, you are required to input below script/code to avoid Quartus from generating an error due to incomplete SmartVID settings.

You may change the scripts listed below in you project QSF file.

Please ensure that there are no other similar settings with different values.

For more information you may refer to below link:

Intel® Agilex™ F-Series FPGA Development Kit User Guide - 6.1. Add SmartVID settings in the QSF file

Please try this step and let me know if error still happen.

Thank you.

Best Regards,

ZulsyafiqH_Intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Shubhangi,

Thank you for your reply.

Apologize for the delayed response as we are having some difficulty with our internal system.

Could you share with us your .qar file?

We are trying to replicate the error from our side.

Best Regards,

ZulsyafiqH_Intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Shubhangi,

Good day.

I wish to follow up with you on this Case.

Could you share with us your .qar file?

We are trying to replicate the error from our side.

Thank you.

Best Regards,

ZulsyafiqH_Intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Shubhangi,

We do not receive any response from you for more than a week to the previous reply that I have provided.

With that, this thread will be transitioned to community support.

If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread.

Thank you.

Best Regards,

ZulsyafiqH_Intel

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page