- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm working on my first FPGA design and hope to get some suggestions. The Avalon bus spec is fairly clear to me, and I've used QSys to create and connect custom components. Higher-level design patterns are where my awareness is lacking.

- Device is Cyclone 10 LP

- Clock speed is 50 MHz

- I am acquiring about 50 channels of data in parallel

- When a channel is active a new 16 bit value is output no more than every 400 uS

- Typically no more than 8 channels are active at a time but the system should be able to capture all

- Each channel component can wait until data is read before continuing the next sample cycle

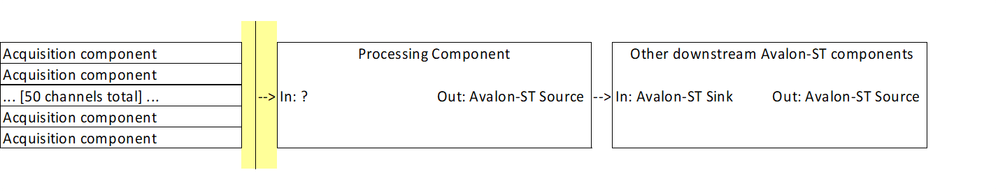

The component to acquire each channel of data is done and works fine in simulation and hardware. I now need to multiplex 50 components' data output into a processing component. The processing component will then expose an Avalon-ST source for downstream components to consume its data. I'm unclear/undecided on a reasonable approach to do this.

High level guidance / suggestions are appreciated. I can see either programming a mux / arbiter in HDL, or trying to use QSys to do it at a higher level. For the QSys route is it even feasible?

How would you typically approach getting many channels of data serialized onto the Avalon bus?

This is a proof of concept and performance / resource efficiency are not important at this stage. Simplicity of understanding, design, and testing is a better target.

Thanks,

Paul

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

This could all be done in Platform Designer (formerly known as Qsys). The inputs can be physical and/or logical (using the channel signal) Avalon-ST channels. Platform Designer includes Avalon-ST components, including mux/demux, for routing data.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page