- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello expert,

We build an Arria10(GX) PCIe Card, which inserts into x86 SERVER for usage. Now we need to realize the FPGA upgrading functionality throught PCIE slot, instead if JTAG coz customer don't have jtag box at all.

Is there any A10 design example to implement this upgrading functionality? Thanks a lot

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I can access the link and download the example design. Kindly try to access using different browser or clear the browsing data history before downloading the design.

Thanks.

Best regards,

KhaiY

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Could you share what does functionality upgrade mean?

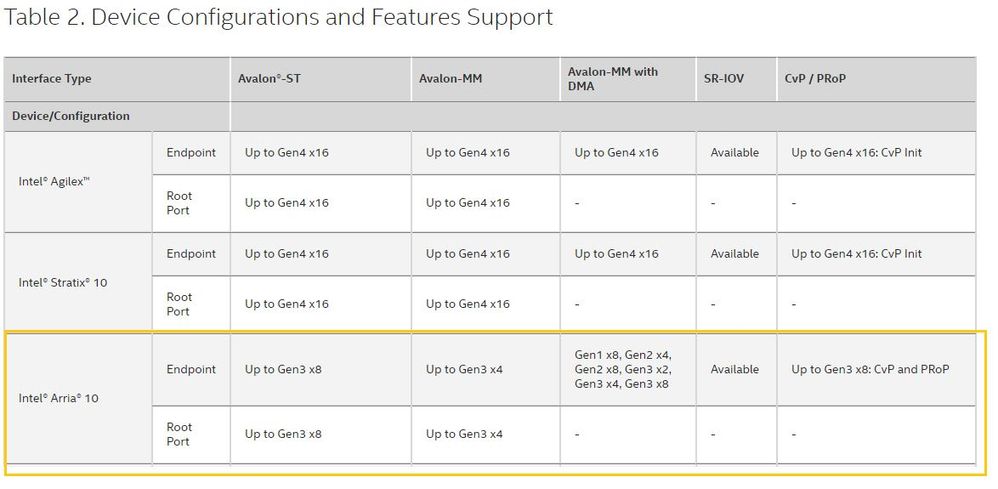

The support feature for Arria 10 is as below

Link: https://www.intel.com/content/www/us/en/programmable/support/support-resources/support-centers/pcie-support.html (Device Selection)

If you go to the User Guide section, you can find the document for each supported feature. You will find the steps to generate the example design in the document.

Thanks.

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @KhaiChein_Y_Intel ,

regarding of " Could you share what does functionality upgrade mean? " question?

=> actually what I mean is :

we want to download & burn new FPGA Image into our A10 board, through PCIe i/f.

I see there're some RSU Example is through “i2c” or "uart" , not sure whether RSU can go through PCIe ? if yes, where can find the example project ?

Thanks for reply

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

For Intel Arria 10 devices, use Partial Reconfiguration over Protocol instead of CvP Update. You can use the PCIe bus to perform Partial Reconfiguration.

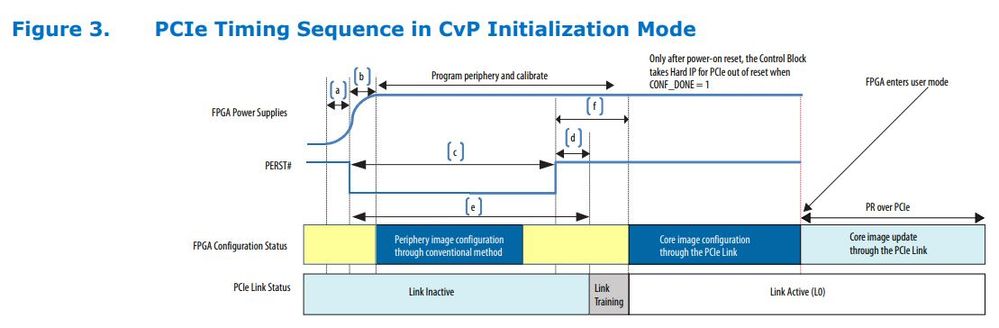

In CvP, you partition your design into two images: core image and periphery image.

- Periphery image (*.periph.jic) — contains general purpose I/Os (GPIOs), I/O registers, the GCLK, QCLK, and RCLK clock networks, and logic that is implemented in hard IP such as the JTAG interface, PR block, CRC block, Oscillator block, Impedance control block, Chip ID, ASMI block, Remote update block, Temperature sensor, and Hard IP for PCI Express IP Core. These components are included in the periphery image because they are controlled by I/O periphery register bits. The entire periphery image is static and cannot be reconfigured.

- Core image (*.core.rbf) — contains logic that is programmed by configuration RAM (CRAM). This image includes LABs, DSP, and embedded memory. The single static core image may include PR reconfigurable regions.

- Reconfigurable region — This region can be programmed in user mode while the PCIe link is up and fully enumerated. It must contain only resources that are controlled by CRAM such as LABs, embedded RAM blocks, and DSP blocks in the FPGA core image. It cannot contain any periphery components such as GPIOs, transceivers, PLL, I/O blocks, the Hard IP for PCI Express IP Core, or other components included in the periphery image.

- Static region — This region cannot be modified.

If you refer to the PCIe timing sequence in CvP mode, you will see that PCIe link is inactive during Periphery image configuration. PCIe link training happens after the Periphery image configuration is completed. Therefore, you can use the PCIe link to perform Core image configuration only. For Periphery image configuration, you have to use the conventional method such as JTAG.

intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug_a10_cvp_prop.pdf

Thanks

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @KhaiChein_Y_Intel ,

thanks for detailed explanation.

unfortunately we FPGA doesn't divided into peri + core 2 parts, our FPGA has only one image, And actually we want is sth like "RSU over PCIE" . right ?

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Referring to Table 92 Configuration Schemes and Features of Intel Arria 10 Devices

A10 support PCIe CvP configuration but it is for core image configuration only.

Thanks

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I’m glad that your question has been addressed, I now transition this thread to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you.

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello @KhaiChein_Y_Intel ,

Sorry but this problem is still there.

I searched and found today Intel FPGA WiKi has released a new example project which may be what I'm seeking, see below :

[ Design Example: Intel Arria 10 FPGA Remote System Update via PCI Express*

]

The problem I'm facing is: when I happily click the " design example link " at " Intel Arria 10 FPGA Remote System Update via PCI Express* | Design Store for Intel® FPGAs ", The page link (https://fpgacloud.intel.com/devstore/platform/20.4.0/Pro/intel-arria-10-fpga-remote-system-update-via-pci-express/) just show [

403: Access Denied

]

Where Can I donwload this " " Intel Arria 10 FPGA Remote System Update via PCI Express* | Design Store for Intel® FPGAs " example project ?

Thanks for help again !

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I can access the link and download the example design. Kindly try to access using different browser or clear the browsing data history before downloading the design.

Thanks.

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I’m glad that your question has been addressed, I now transition this thread to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @KhaiChein_Y_Intel ,

We have been trying to be able to perform remote system update of Arria 10 GX FPGA

Our setup is as below:

- Arria 10 GX development board connected as a PCIe device to the motherboard of a PC having Intel i5 processor.

- OS installed on host PC : Ubuntu 20.04 64-bit

We have loaded the RSU over pcie example design provided by Intel on the FPGA.

However, when we run the `lspci -v` command on a terminal in the host PC as a root user, we get the below output,

------------------------------------------------------------------------------------------

01:00.0 Unassigned class [ff00]: Altera Corporation Device e001 (rev a5)

Subsystem: Device a106:2484

Flags: fast devsel, IRQ 11

Memory at <unassigned> (64-bit, prefetchable) [disabled]

Capabilities: [50] MSI: Enable- Count=1/4 Maskable- 64bit+

Capabilities: [78] Power Management version 3

Capabilities: [80] Express Endpoint, MSI 00

Capabilities: [100] Virtual Channel

Capabilities: [200] Vendor Specific Information: ID=1172 Rev=0 Len=044 <?>

Capabilities: [300] Secondary PCI Express

Capabilities: [800] Advanced Error Reporting

Kernel modules: altera_cvp

------------------------------------------------------------------------------------------

Would you please give any input(s) with regard to addressing the above issue?

Thanks in advance.

- Sachin

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page