- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Using Cyclone 3 and Quartus 13.1.

The result is PLL changes clock speed to wrong value (much slower that should be), scandone goes high, and PLL does not lock.

What I do:

1. In megawizard configure PLL the way I need, save it, open it again in megawizard, and use "generate configuration file" having MIF file created for present configuration.

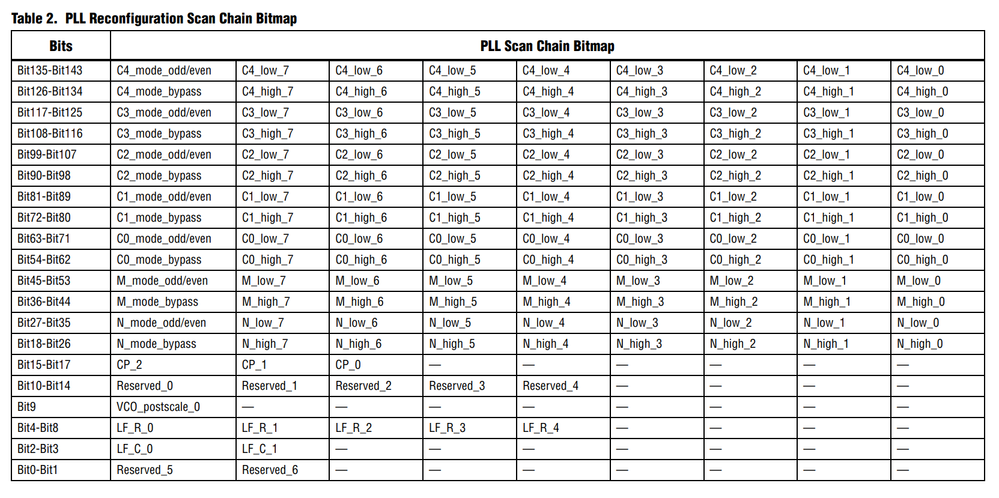

2. When reconfiguration is needed I shift 144 bits in the order from 0 to 143 (as in MIF file), through scandata, clock is controlled by scanclkena.

3. Wait one reconfiguration clock cycle, and activate configupdate for one clock cycle.

4. independently of actions above watch for scandone, and on second clock after its falling edge reset PLL using areset having it active for one clock cycle.

What is wrong? I checked shifting data in correct direction from bit 0 to 143, I checked it takes 144 cycles to shift, thus data must be in PLL. But still it starts with wrong frequency and never gets done.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I found the solution to the problem. Information is buried in ALTPLL and ALTPLL_RECONFIG documents in different places, people who do not have deep overview of the architecture would hardly match different, but related pieces of info. For cyclone 3 I must activate PLL areset pin for one reconfig clock cycle after PLL raises scandone.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Found the problem for wrong frequency. I was shifting bit 0 first. Manual says it must be bit 143 first. Kind of against logic, but why not.

However scandone is still always high after first reconfiguration. At the same time PLL locks, and everything else seems to be ok. Checked with scope, output frequencies are correct. Tried Modelsim (it is stupid not loading MIF files - thus used scan chain filled with 0s) - it also shows scandone going up and never getting low, however manual says that it must deactivate as soon as reconfiguration is complete.

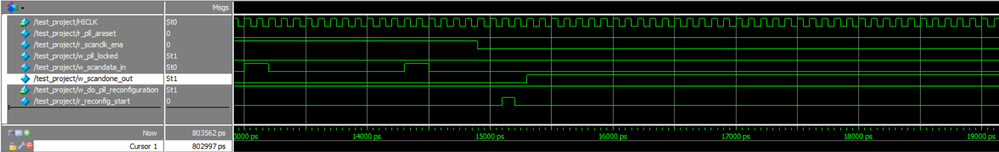

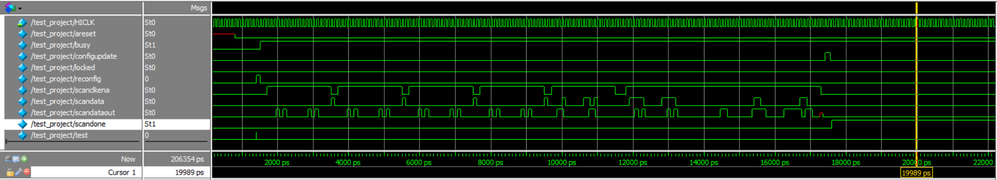

Above shows the completion of the scan line write and reconfiguration

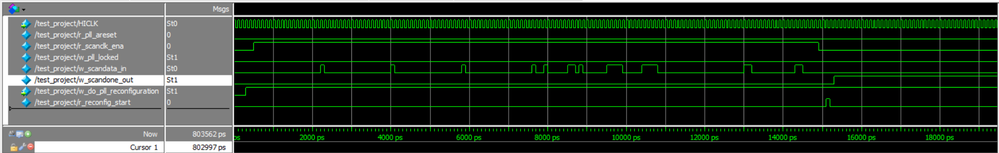

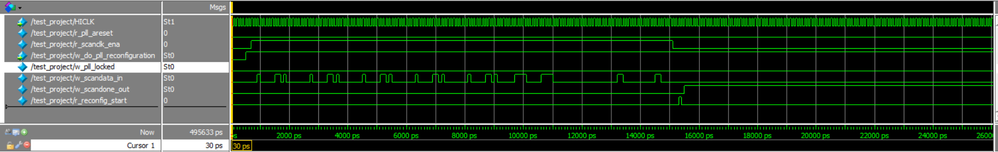

The above shows whole operation. I managed to load proper .HEX file into ROM in Modelsim, and as we see `scandone` goes high and does not fall back low in simulation (as well as in real system). Lock goes high in some time (not shown on the picture).

You can see that c4-c1 are loaded with zero counters, only c0 is being initialized.

Above picture: putting same "valid" settings to all the PLL channels does not make difference - scandone still does not return low.

Unfortunately the list of registers above does not have any enable/disable bits for specific PLL outputs (like we have checkmarks in megawizard). May loading zeroes into the counter prevent scandone to complete?

Can not get what I am doing wrong here.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have made design using ALTPLL_RECONFIG and its simulation behaves the same erratic way - scandone goes high and does not get back low - with busy stuck high.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I found the solution to the problem. Information is buried in ALTPLL and ALTPLL_RECONFIG documents in different places, people who do not have deep overview of the architecture would hardly match different, but related pieces of info. For cyclone 3 I must activate PLL areset pin for one reconfig clock cycle after PLL raises scandone.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Just saw your thread. Looks like you managed to resolve the issue on your own. As you correctly pointed out, areset signal is important to be asserted and deasserted.

Regards

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page