- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

When instantiating simplex Rx and Tx JESD cores generated by quartus, and enabling the reconfiguration interfaces, the following placement error shows:

Error (12829): Failed to merge HSSI Avalon Memory-Mapped interface instances "main|devices[0].jesd204_rx_core|main|intel_arria_10.unit|intel_jesd204_core|jesd204_core|jesd204_0|inst_phy|inst_xcvr|g_xcvr_native_insts[1].twentynm_xcvr_native_inst|twentynm_xcvr_native_inst|inst_twentynm_xcvr_avmm|avmm_atom_insts[0].twentynm_hssi_avmm_if_inst" and "main|devices[0].jesd204_tx_core|main|intel_arria_10.unit|intel_jesd204_core|jesd204_core|jesd204_0|inst_phy|inst_xcvr|g_xcvr_native_insts[1].twentynm_xcvr_native_inst|twentynm_xcvr_native_inst|inst_twentynm_xcvr_avmm|avmm_atom_insts[0].twentynm_hssi_avmm_if_inst" into single Avalon Memory-Mapped Interface.

The error is also described here, albeit for a different IP, but still the error is the same..

Another similar issue is here, which does seem to have a workaround

So is there a workaround for my case as well, or is upgrading to latest quartus really necessary, and how do I know that this will in fact solve the issue without having to upgrade the entire design?

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

As I understand it, you encounter some issues when trying to place two simplex JESD instances into the same XCVR channel. To ensure we are on the same page, just would like to check with you on the following:

1. What is the device that you are using?

2. What is the Quartus version that you are using?

3. Are you using JESD204B or JESD204C IP?

4. Would you mind to share with me a simple test design with only the JESD instances which could replicate the error to facilitate further debugging.

Please let me know if there is any concern. Thank you.

Best regards,

Chee Pin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

Hi that is correct.

Please see answers below

1. What is the device that you are using?

Arria 10

2. What is the Quartus version that you are using?

17.1 Pro

3. Are you using JESD204B or JESD204C IP?

JESD204B

4. Would you mind to share with me a simple test design with only the JESD instances which could replicate the error to facilitate further debugging.

Design is integrated in our top level can't share this, but attached a JESD Rx simplex and JESD Tx simplex example designs with their reconfiguration interfaces enabled and which also exhibit this issue. If you try to place JESD Tx and JESD Rx in same bank and transceiver channel, the error shows up.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Sorry for the delay. Thanks for sharing the designs. Please allow me some more time to debug into this. Please ping me if you do not hear from me by end of the week.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

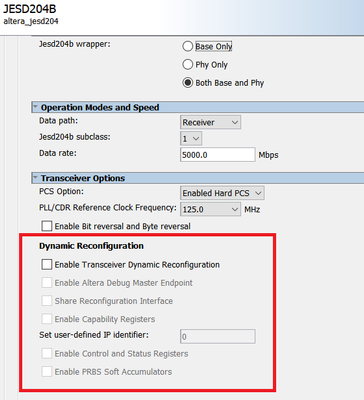

For your information, I have created a simple test design with simplex JESD204b TX and RX PHY only with dynamic reconfiguration enabled. I was able to merge both into the same XCVR channel. Attached is the QAR for your reference. Note that I am using PHY only to ease the demo.

For your information, you should take note that you cannot merge if you have the following enabled:

1. ADME

2. Shared reconfig interface

3. Capability registers

I believe you cannot enable the Control and status registers and PRBS soft accumulators as well but I could not be sure on these two. You may further test out if you need these.

Please let me know if there is any concern. Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Thanks for your message, but still no success.

I did find this explanation on the error message here as well

which is quite similar.

My flow uses tcl scripts, and when I write out the .tcl file for IP generation during the build phase, the only options I see are the following:

set_instance_parameter_value jesd204_0 {TEST_COMPONENTS_EN} {0}

set_instance_parameter_value jesd204_0 {bitrev_en} {0}

set_instance_parameter_value jesd204_0 {bonded_mode} {non_bonded}

set_instance_parameter_value jesd204_0 {gui_analog_voltage} {1_0V}

set_instance_parameter_value jesd204_0 {gui_user_crete_tile} {etile}

set_instance_parameter_value jesd204_0 {lane_rate} {9830.4}

set_instance_parameter_value jesd204_0 {pll_reconfig_enable} {0}

set_instance_parameter_value jesd204_0 {pll_type} {CMU}

set_instance_parameter_value jesd204_0 {rcfg_enable_split_interface} {0}

set_instance_parameter_value jesd204_0 {rcfg_jtag_enable} {0}

set_instance_parameter_value jesd204_0 {rcfg_shared} {0}

set_instance_parameter_value jesd204_0 {sdc_constraint} {1.0}

set_instance_parameter_value jesd204_0 {set_capability_reg_enable} {0}

set_instance_parameter_value jesd204_0 {set_csr_soft_logic_enable} {0}

set_instance_parameter_value jesd204_0 {set_prbs_soft_logic_enable} {0}

set_instance_parameter_value jesd204_0 {set_user_identifier} {0}

set_instance_parameter_value jesd204_0 {wrapper_opt} {base_phy}

set_instance_property jesd204_0 AUTO_EXPORT true

and they are all disabled...But it still shows the error message.

I also saw that your design only has 1 JESD lane, my design has 2 lanes...could that be interfering as well?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Just to follow up with you on this. Please let me know if there is any concern. Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Can you try using the IP Editor flow to see if there is any difference?

Also, just would like to check with you if you are using E-Tile device? I saw the following:

set_instance_parameter_value jesd204_0 {gui_user_crete_tile} {etile}

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

This .tcl file is generated from within the IP generator by writing it out from there...

This ticket also mentions to disable those things.

Workaround/Fix

To avoid this error, option "NPDME", "optional reconfiguration logic" or "embedded reconfiguration streamer" need to be disabled in the Native PHY IP.

But how can you disable this on JESD IP generation, as it creates wrappers for core + transceiver PHY?

The device we use is the 10AS057H3F34E2SG

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

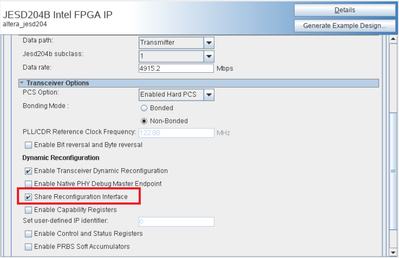

Hi,

Regarding your latest inquiries on the dynamic reconfiguration options in the JESD204B IP, you can control these option at the IP Editor. Note that you might observer "Share reconfiguration interface" is ON and greyed out. As a workaround, you can set ON dynamic reconfiguration, set the number of lane = 2, then turn OFF the "Share reconfiguration interface". Then set the number of lane = 1. Please let me know if there is any concern. Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Does this disable "optional reconfiguration logic" or "embedded reconfiguration streamer?

Those are not options on the IP. I suppose the Debug MAster Endpoint is equivalent to NPDME.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

If you require dynamic reconfiguration, I would recommend you enable only the Transceiver Dynamic Reconfiguration option only and leave the rest unchecked. Then try again with the merging. You can refer to the previous example design which I shared to you for further details.

Please let me know if there is any concern. Thank you.

Best regards,

Chee Pin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm afraid this still doesn't work for me.

Please see attached .ip files how they are included and built in the project.

These seem to have all the correct settings as you describe

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for sharing the files. For your information, as I look into your IP configuration, I notice that you have enabled the "Shared Reconfiguration Interface" in both of your TX and RX instances. As I mentioned in one of my previous note, you can only merge if this option is disabled. Can you try disabling this option and also use 1 lane to ease the testing? Please feel free to keep me posted on the test result.

Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I have also disabled this, and still doesn't work.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for your update. I have updated test design which is having one lane Base & PHY TX only and RX only instances which are able to merge. You may take a look into it and customize from there. Note that this design is created with A10 device and Q17.0Std installed in my local PC.

Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello again

I am again attaching my files, as this is really not working.

Can you please try my configuration? Your configuration only shows 1 lane per converter device.We are using multiple lanes

The parameters are all exactly the same, with only Dynacmi Reconfiguration ticked.

All others are off. The only differences now are that my IP uses more lanes.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

These are my pin assignments

set_location_assignment PIN_T28 -to "jesd204b_a_ref_clk"

set_location_assignment PIN_T27 -to "jesd204b_a_ref_clk(n)"

set_location_assignment PIN_V9 -to "jesd204b_a_sysref"

set_location_assignment PIN_V8 -to "jesd204b_a_sysref(n)"

set_location_assignment PIN_P32 -to "jesd204b_a_rx[0]"

set_location_assignment PIN_P31 -to "jesd204b_a_rx[0](n)"

set_location_assignment PIN_M32 -to "jesd204b_a_rx[1]"

set_location_assignment PIN_M31 -to "jesd204b_a_rx[1](n)"

set_location_assignment PIN_L34 -to "jesd204b_a_tx[0]"

set_location_assignment PIN_L33 -to "jesd204b_a_tx[0](n)"

set_location_assignment PIN_G34 -to "jesd204b_a_tx[1]"

set_location_assignment PIN_G33 -to "jesd204b_a_tx[1](n)"

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

And I've also added this assignment, but with or without this doesn't help

set_instance_assignment -name XCVR_RECONFIG_GROUP merge_jesd_0 -to jesd204b_a_rx[0]

set_instance_assignment -name XCVR_RECONFIG_GROUP merge_jesd_0 -to jesd204b_a_tx[0]

set_instance_assignment -name XCVR_RECONFIG_GROUP merge_jesd_1 -to jesd204b_a_rx[1]

set_instance_assignment -name XCVR_RECONFIG_GROUP merge_jesd_1 -to jesd204b_a_tx[1]

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Sorry for the delay. For your information, I have created a simple test design with mimic your configuration in A10 and able to merge the TXs and RXs in Q17.0Std. I have attached the QAR for your reference as well.

Please let me know if there is any concern. thank you.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page