- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

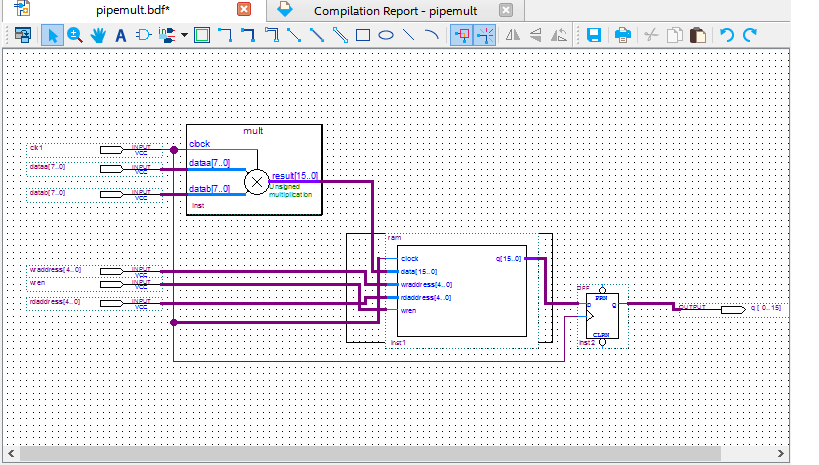

Error (12153): Can't elaborate top-level user hierarchy

Error: Quartus Prime Analysis & Synthesis was unsuccessful. 2 errors, 2 warnings

Can anyone please help me understand what exactly I should do to rectify it?

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Check the connections of clock,wren(need to be wire) of ram instance & PRN, CLRN should connect inputs using pin tool.

please let me know if you have any different concern.

Regards,

Vicky

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Just to explain a bit clearer, you have clock and wren connected as busses (thick lines) instead of individual wires (thin lines). Delete the busses and use the wire tool to make the connections. Also, the reset input into the register (CLRN) should be hooked up as well, either to an I/O pin or perhaps even just pulled high.

#iwork4intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes. I tried that too, I just had some problems with installation. Once I re-installed the software it worked fine. Thanks !

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Can you share the source codes files for this or link for the same?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page