- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

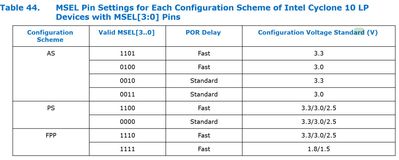

Can the configuration bank on a cyclone 10 LP bet set at 1.8V when using Passive Serial configuration? Table 44 in the Core fabric handbook (c10lp-51003.pdf) suggests that the Configuration Voltage Standard is limited to 3.3V/3.0V/2.5V. A Host device would be driving the PS bus with 1.8V logic.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Apologize that it cannot be. Configuration bank (I/O banks 1, 6, 7, and

The reason is that it will affect the device bootup and configuration.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I've run into the same issue with using passive serial but trying to drive it with 1.8V from a host processor. Looking through the documentation and device pinout spreadsheet it's not clear to me why bank 7 also needs to be configured for 3.3/3.0/2.5V. Can you confirm that bank 7 requires 3.3/3.0/2.5V for PS configuration?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page