- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am using Cyclone-IVE FPGA (EP4CE55F23C8N).

I was tryinng to figure out what source series termination I should use for I/Os in 3.3V powered bank.

The required I/O standard is LVCMOS 3.3V. In the IBIS model, I was able to find cmos33_cio_d2.

(1) What is the significane of the term d2 in cmos33_cio_d2?

(2) What is the drive strength in this model - I need to simulate it in 12mA drive strength and slow, but I am not seeing any such option.

(3) When I use this model as output in Hyperlynx VX2.7, I am getting the driver output resistance greater than 50 ohms. What is happening?

Thanks n Regards,

Binayak

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

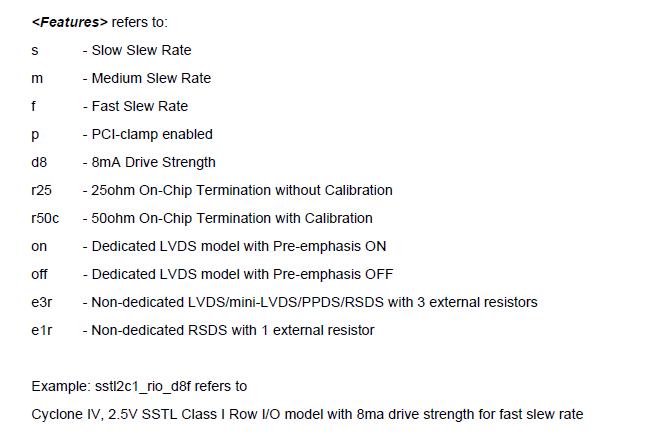

The term cmos33_cio_d2 is (in a_b_c form):

a. 3.3 LVCMOS

b. Column IO

c. 2mA drive strength.

The term d2 stands for drive strength of 2mA in this model. May I know how did you get driver output resistance?

Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Amit,

You can approximate the output resistance as follows:

- Simulate the open-ended driver with a step edge.

- Now connect the driver to ground through a series resistor Rs.

- Now sweep the Rs value such that the output voltage level with the resistor is half of the voltage level we got when simulating with just the driver. The value of Rs in such case is equal to the output resistance of the driver.

(1a) Is the process that I described correct? If not, what is the correct process to determine output resistance of the driver?

(1b) From the output resistance calculation as described above, the output resistance for cmos33_cio_d2 is coming more than 50 ohms. In such case, can we use source series termination? If yes, what value would you use because for 50 ohms characteristics impedance (Zo), Rs = Zo - Rdriver.

(2) So as per your reply, does it mean that the maximum drive strength of 3.3V LVCMOS is only 2mA? This is weird as this value is too small. We normally have lvcmos drive strength as 8mA or 12mA as typical values for driving 50 ohm transmission lines.

Thanks n Regards,

Binayak

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

(1a) Is the process that I described correct? If not, what is the correct process to determine output resistance of the driver?

(1b) From the output resistance calculation as described above, the output resistance for cmos33_cio_d2 is coming more than 50 ohms. In such case, can we use source series termination? If yes, what value would you use because for 50 ohms characteristics impedance (Zo), Rs = Zo - Rdriver.

May I know how did you get this resource to determine the output resistance of the driver? You may use source series termination under certain conditions. You may refer more details on this document: https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/cyclone-iv/cyiv-51006.pdf

(2) So as per your reply, does it mean that the maximum drive strength of 3.3V LVCMOS is only 2mA? This is weird as this value is too small. We normally have lvcmos drive strength as 8mA or 12mA as typical values for driving 50 ohm transmission lines.

The d2 in the acronym means 2mA drive strength for fast slew rate. You can view the naming method from Cyclone IV Models User Guide from this link: https://www.intel.com/content/www/us/en/programmable/support/support-resources/download/board-layout-test/ibis/ibs-ibis_index.html

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Please see my reply inline to your follow-up questions.

(1a) Is the process that I described correct? If not, what is the correct process to determine output resistance of the driver?

(1b) From the output resistance calculation as described above, the output resistance for cmos33_cio_d2 is coming more than 50 ohms. In such case, can we use source series termination? If yes, what value would you use because for 50 ohms characteristics impedance (Zo), Rs = Zo - Rdriver.

May I know how did you get this resource to determine the output resistance of the driver? You may use source series termination under certain conditions. You may refer more details on this document: https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/cyclone-iv/cyiv-51006.pd...

[Binayak]: It's just based on simple voltage divider electrical circuit. Say a 3.3V driver outputs a 3.3V step edge. It will produce a step edge of half of 3.3V (1.65V), when you add an external series resistor equal to the output resistance of the driver inside the chip.

(2) So as per your reply, does it mean that the maximum drive strength of 3.3V LVCMOS is only 2mA? This is weird as this value is too small. We normally have lvcmos drive strength as 8mA or 12mA as typical values for driving 50 ohm transmission lines.

The d2 in the acronym means 2mA drive strength for fast slew rate. You can view the naming method from Cyclone IV Models User Guide from this link: https://www.intel.com/content/www/us/en/programmable/support/support-resources/download/board-layout...

[Binayak]: I have seen the I/O tables. The 3.3V LVCMOS only has drive strength of 2mA. Really don't know how you can drive 50 ohms transmission lines such low drive strength.

Thanks n Regards,

Binayak

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Binayak,

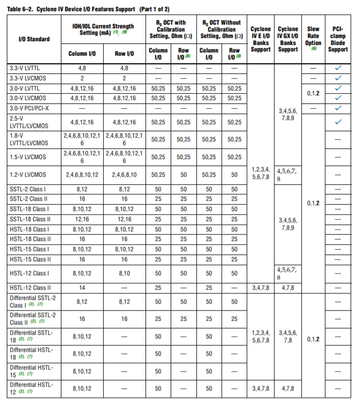

The output buffer for each Cyclone IV I/O pin has a programmable current strength

control for certain I/O standards. The supported settings ensure that the device driver

meets the specifications for IOH and IOL of the corresponding I/O standard to decrease the effects of simultaneously switching outputs (SSO) in conjunction with reducing system noise.

When you use programmable current strength, on-chip series termination (RS OCT) is

not available

The default current strength setting in the Quartus II software is 50-ohm OCT without calibration for all non-voltage reference and HSTL/SSTL Class I I/O standards. The default setting is 25-ohm OCT without calibration for HSTL/SSTL Class II I/O standards.

This table might be helpful for you

Thank you.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page