Hi,

I'm currently trying to get a Cyclone V 5CEFA9U19C8 FPGA to boot via Active Serial using the MX25L12833FM2I-10G chip. Based on the datasheet, this chip is the 8-Pin SOP version of the MX25L12833FMI-10G, which I have previously tested successfully.

So far, I have attempted configuration with Active Serial x1 and x4 using the MX25L128 configuration preset in 'Convert Programming Files'. Neither of these has allowed the device to boot. In both configurations, I am able to read back the jic from the SPI rom and verify that the retrieved image is identical to the written image.

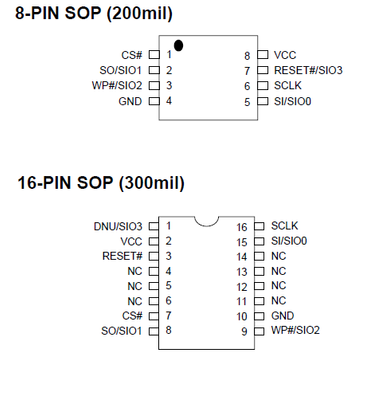

I suspect it may be due to slight differences in the pinout - the MX25L12833FM2I has both SIO3 and Reset on the same pin, while the MX25L12833FMI has a separate reset pin. Our design has SIO0-SIO3 all connected to the FPGA, so I'm not sure if at some point during the boot process, prior to entering QSPI mode, the SIO3 is pulled low (which would reset the ROM and potentially interrupt the load).

Below are the pinouts of the two variants for reference.

The steps I have tried so far are:

- Use active serial x4 and x1 (Failed) for .jic

- Disconnect SIO3/Reset pin and use active serial x1 (Failed)

- Modify our internal IP cores (Remote Update) so that it uses an MX25L128 instead of the default EQPC128.

- Modify though assignments -> device -> device and pin options to use Active Serial x1 + Auto flash type.

链接已复制

Hi, apologize that we have tested only MX25L12833FMI-10G. Meanwhile for MX25L12833FM2I-10G, it could be the issue. I would suggest reading out the signal from all the data pin and see where it stuck at.

For non-supported flash, I would suggest to create the programming file using our generic flash programmer. You may refer to link below:

Will do, thank you. Is there anything I should be looking for to determine where it gets stuck? My immediate thought is to run a trigger on nStatus to see when it goes LOW and see what commands are being run prior.

Hi,

I tried checking the n_status signal and it never seems to go low. Once a configuration error occurs, is it held low, or does it come back up? Would imagine if the latter happens, it would still trigger a falling edge on the logic analyzer, but I do not see anything

You need to turn on the Auto-restart configuration after error option in the General page of the Device and Pin Options dialog box in the Intel Quartus Prime software in order for n_status signal to come back up, else it will remain low after configuration error.