- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

We are using Cyclone V (5CGXFC7B6M15I7N) in on of our design. We are doing the timing budget analysis for QSPI NOR Flash interface (AS Configuration). FPGA datasheet shows the DATA[] hold time after rising edge on DCLK as '0 nS' (Page 76). Request you to provide the minimum hold time the FPGA holds the data after the DCLK rising edge, which will be helpful for the setup and hold time margin calculations with the Flash device.

Thanks

Sudheer.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sudheer,

You can use the 1.5nS. That will also protect you if you need to change to EPCQ-A device in the future because the EPCQ device is EOL (https://www.mouser.com/pcn/intel_corporation_pdn1708_rev_1.0.0.pdf).

There is not much functional difference between the two. I think Intel's supplier for EPCQ shut down so they had to create a new part and called it EPCQ-A.

Thanks,

Travis

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sudheer,

Please refer to the Device Handbook in the section on Evaluating Data Setup and Hold Timing.

Cyclone V Device Timing: https://www.intel.com/content/www/us/en/docs/programmable/683801/current/active-serial-as-configuration-timing.html

Here is a migration guide that can also help. https://www.intel.com/content/www/us/en/docs/programmable/683340/current/fpga-configuration-device-migration.html

Be careful when calculating the hold time. You might need to add a 10pF capacitor on the data lines if you cannot meet the hold time in the calculation.

If you look at the timing waveforms, the data is captured on the falling edge.

Thanks,

Travis Covert

travis.covert@arrow.com

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Travis,

Thanks for the update.

We have gone through the documentation that you have sent. We have calculated the data setup and hold time margins at FPGA.

To calculate the setup and hold time margins at the QSPI Flash we need the minimum data hold time requirement of the FPGA (During Flash Write cycle), which we are not able to get from the datasheet.

Thanks

Sudheer

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sudheer,

For Flash Write operations the timing diagram should be in the flash datasheet.

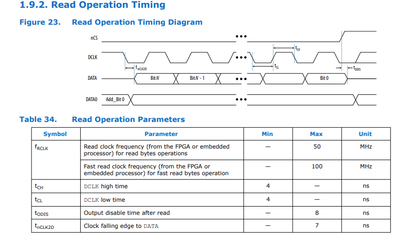

Here is the timing waveform for the EPCQ flash.

Thanks,

Travis

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Travis,

Thanks for your reply. We are using EPCQ64SI16N in our product.

The read operation timing doesn't specify the minimum data hold time (after clock falling edge) requirement for data in the datasheet. Can you please help to provide this value. Datasheet gives only clock falling edge to data valid time.

Thanks

Sudheer

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sudheer,

The rising edge data is in the EPCQ datasheet. The falling edge data is in the FPGA handbook, linked below.

The falling edge information is in the Cyclone V handbook. Please refer to the Device Handbook in the section on Evaluating Data Setup and Hold Timing.

Hope this helps.

Travis

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Travis,

We have checked the FPGA hold up time from handbook. We are looking for the hold up time information from Flash side. Here i have attached the datasheet snapshots from Micron NOR flash (MT25QU512ABB8E12-0AUT TR). We need the similar timing information for the EPCQ64SI16N device.

Request you to check this and provide the information.

Thanks for your quick reply.

Thanks

Sudheer

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sudheer,

That Micron flash supports Double Data Rate (read data on rising and falling edges). EPCQ does not.

Since the EPCQ does not read data on the falling edge, it does not care about the timing of the data signals on the falling edge.

The EPCQ reads data signal in WRITE mode so there are timing specs for rising edge in the EPCQ datasheet. However, the FPGA reads data signals during READ mode, and it reads the data on the falling edge. This is why there is timing data around the falling edge but not the rising edge in the FPGA datasheet.

Thanks,

Travis

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Travis,

Thanks for the clarification.

In the Intel APP note AN822 (FPGA Configuration Device Migration Guideline), to find the hold timing slack below formula is given.

tBT_DCLK + tCLQX + tBT_DATA >= tDH. I have attached here the snapshot of the App note.

We have the values for tBT_DCLK and tBT_DATA from the trace length calculations. (~0.2nS)

We have the tDH value from Cyclone V datasheet. (2.9nS)

We believe tCLQX to be obtained from Flash datasheet, but we donot see the value of tCLQX from Configuration Flash (EPCQ64SI16N ).

Any recommended value for this parameter tCLQX from intel, will help us defining the hold timing slack in our design.

Thanks

Sudheer

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sudheer,

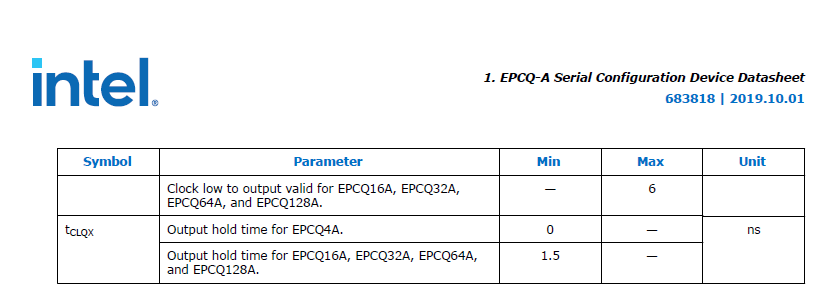

Here is a screenshot of the output hold time.

Thanks,

Travis

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Travis,

Looks like the snapshot you have provided is for the EPCQ64A devices with 1.5nS output hold time. We are using EPCQ64SI16N without 'A' suffix.

Can we use 1.5nS output hold time for EPCQ64SI16N as well?

Can you please elaborate what is the difference between EPCQ64A and EPCQ64 devices?

Thanks

Sudheer

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sudheer,

You can use the 1.5nS. That will also protect you if you need to change to EPCQ-A device in the future because the EPCQ device is EOL (https://www.mouser.com/pcn/intel_corporation_pdn1708_rev_1.0.0.pdf).

There is not much functional difference between the two. I think Intel's supplier for EPCQ shut down so they had to create a new part and called it EPCQ-A.

Thanks,

Travis

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks Travis for the information.

This concludes our discussion.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I’m glad that your question has been addressed, I now transition this thread to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page