- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I want to do an discrete RSU with UART interface. I wrote the UART, RAM and on-chip memory in VHDL but how can I write dualboot and user logic of RSU. There is an atom for RSU implementation published by Intel but all my works are in VHDL, so how can I convert this into VHDL or I can run this on VHDL based project?

fiftyfivenm_rublock <rublock_name>

(

.clk(<clock source>),

.shiftnld(<shiftnld source>),

.captnupdt(<captnupdt source>),

.regin(<regin input source from the core>),

.rsttimer(<input signal to reset the watchdog timer>),

.rconfig(<input signal to initiate configuration>),

.regout(<data output destination to core>)

);

defparam <rublock_name>.sim_init_config = <initial configuration for simulation only>;

defparam <rublock_name>.sim_init_watchdog_value = <initial watchdog value for simulation only>;

defparam <rublock_name>.sim_init_config = <initial status register value for simulation only>;Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

You will need to instantiate the IP as a verilog module before you are able to instantiate the the verilog module in VHDL. https://www.intel.com/content/www/us/en/programmable/support/support-resources/knowledge-base/solutions/rd11162011_444.html

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I try this but I cannot do that because for creating a component we need the signals types and lengths and I don't know these signals' informations just their names. Addition to this I'm still very shocked about how Intel's documentations in discrete RSU is realy bad even there is no documentation and when I ask about this topic this forum didn't tell me anything except I already know.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Exactly, I am trying to make discrete RSU logic for months, as an intern in a company. I am not sure is this a suitable project for an intern or not but I do have hard times. AN741 documentation is just for Nios II, just the video mention discrete logic yet some sentences. I will use On-Chip Flash IP Core, and UART core. I should design the state machine myself. The on-chip IP user guide is well-documented but UART is not. I could not find how to access the registers inside the UART core. By the way, I will not use Dual-Configuration IP logic, since I will delete the CFM first and put the new image to CFM. That's why I think I do not need to trigger it since it automatically uses the image that I put in CFM. Am I wrong? Thanks in advance..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

First, you can refer that link for example RSU code with UART: (https://community.intel.com/t5/FPGA-SoC-And-CPLD-Boards-And/Max1000-Remote-System-Upgrade-via-SPI/m-p/1368963/highlight/true#M22012).

Second, you can use this UART core: (https://opencores.org/projects/simple_uart_for_fpga). It is very simple, easy to use and you can control everything.

Third, in fact RSU logic without Nios is not that complex, but lack of documentation complicate it. As you know there are 2 images in MAX10 devices. 2 CFMs for image2 and 1 CFM for image1. Normally if you didn't do contrary, device begins with image1. You can change this with driving config_sel pin physically. If there is no image of one of them, or the image is broken, device begins with solid one. If both of them is broken or not programmed, device cannot begin. Yes you can clear and reprogram the working image when its working, but I think you have to still use the dual IP core. Because device not restarts itself when new CFM image loaded. You do it with IP. Maybe manual power on-off can work either, but in that case of "Remote" System Upgrade, you don't want to do it.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Unfortunately we do not have the timing information on this. You can only get the timing information based on the TimeQuest report.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Timing information? I don't want to know timing information. Where did you get this idea from? I just want to know how I implement the rublock to VHDL or any other way to do discrete RSU.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

May I know what signals types and lengths information that do you need? We only have the port connection information and you should be able to invoke connect it to VHDL.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I would recommend you to generate the Dual Configuration IP in VHDL which will be more easier to use rather than the ATOM module.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

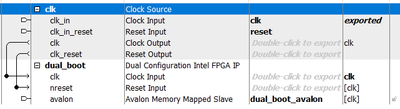

Attach is the IP generated. You can observed that inside the "RU" folder, where RU_inst.vhd is calling RU_inst.v file.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for your reply @JohnT_Intel. I don't know either the signal informations. I just wanted to perform discrete RSU. Also I'm already started to use dual config IP. So far, I'm able to set config_sel and reconfig the device in either CFM0 or CFM1/2. I think this is enough for RSU. But if you know how to do error checking and fallback situations it is also useful for me. But the main issue that I working on now how I can write the .rpd file into CFM sectors. I can use the on-chip flash IP but I don't know the form of data that I write into CFM. Can I write the data as well as in the .rpd file? In AN741 the data's MSB and LSB was swapped, do I have to swap too? I'll use UART interface, the data came as bytes. I'm planning the write the data into RAM first. When the data came, then I'll write it to CFMs. Also for testing I want to initialize the RAM for not doing the data sending stuff for now. So anything you know about my situation will be helpful.

Thanks.

- Tags:

- Thank

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

For the ones who wonder the use of dual boot configuration IP, here is the example VHDL code:

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity manual_rsu is

port(

clk : in std_logic;

reset : in std_logic;

leds : out std_logic_vector(7 downto 0)

);

end entity;

architecture rtl of manual_rsu is

component rsu_pd is

port (

clk_clk : in std_logic := 'X'; -- clk

reset_reset_n : in std_logic := 'X'; -- reset_n

dual_boot_avalon_address : in std_logic_vector(2 downto 0) := (others => 'X'); -- address

dual_boot_avalon_read : in std_logic := 'X'; -- read

dual_boot_avalon_writedata : in std_logic_vector(31 downto 0) := (others => 'X'); -- writedata

dual_boot_avalon_write : in std_logic := 'X'; -- write

dual_boot_avalon_readdata : out std_logic_vector(31 downto 0) -- readdata

);

end component rsu_pd;

signal db_avalon_address : std_logic_vector(2 downto 0) := (others => 'X');

signal db_avalon_read : std_logic := 'X';

signal db_avalon_writedata : std_logic_vector(31 downto 0) := (others => 'X');

signal db_avalon_write : std_logic := 'X';

signal db_avalon_readdata : std_logic_vector(31 downto 0) := (others => '1');

signal cnt : integer := 0;

begin

rsu : component rsu_pd

port map (

clk_clk => clk, -- clk.clk

reset_reset_n => reset, -- reset.reset_n

dual_boot_avalon_address => db_avalon_address, -- dual_boot_avalon.address

dual_boot_avalon_read => db_avalon_read, -- .read

dual_boot_avalon_writedata => db_avalon_writedata, -- .writedata

dual_boot_avalon_write => db_avalon_write, -- .write

dual_boot_avalon_readdata => db_avalon_readdata -- .readdata

);

process (all)

begin

if(reset = '0') then

leds<= "11001100";

cnt <= 0;

elsif(rising_edge(clk)) then

cnt <= cnt + 1;

if(cnt = 0) then

leds <= "00011000";

db_avalon_address <= "001";

db_avalon_writedata <= x"00000001";

-- set config_sel_overwrite and config_sel for boot from CFM0

db_avalon_read <= '0';

db_avalon_write <= '1';

elsif(cnt = 3) then

-- write operation needs 3 cycle

db_avalon_read <= '0';

db_avalon_write <= '0';

elsif(cnt = 4) then

db_avalon_address <= "011";

-- read busy signal

db_avalon_read <= '1';

db_avalon_write <= '0';

elsif(cnt = 5) then

-- read operation needs 1 cycle

db_avalon_read <= '0';

db_avalon_write <= '0';

elsif(cnt = 6) then

-- read data came in 3th cycle

db_avalon_write <= '0';

db_avalon_read <= '0';

leds(0) <= db_avalon_readdata(0);

leds(7 downto 1) <= (std_logic_vector(to_unsigned(cnt, 7)));

elsif(cnt = 7) then

db_avalon_address <= "000";

-- trigger reconfig

db_avalon_writedata <= x"00000001";

-- hold nconfig min 250ns, 4 cycle at 12 MHz

db_avalon_read <= '0';

db_avalon_write <= '1';

elsif(cnt > 7) then

end if;

end if;

end process;

end rtl;

And in platform designer:

You can reach the dual boot IP's addresses and relevant bits from page 62 on:

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/max-10/ug_m10_config.pdf

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

The fallback will automatically happen when the configuration failed. In order to update the CFM then you will need to use the On Chip Flash IP.

You may refer to https://fpgacloud.intel.com/devstore/platform/17.1std.1/Standard/i2c-remote-system-update-example/ on how to implement RSU in Max 10.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

@JohnT_Intel Hi, I am following the example that you mentioned i.e

https://fpgacloud.intel.com/devstore/platform/17.1std.1/Standard/i2c-remote-system-update-example/

Can you point me to Altera example projects that contain the source files(c files) of nios_platform.pof and source files of RSU.sof.

Thanks in Advance.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page