- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

I am trying to emulate the Design Example: Intel Arria 10 FPGA Remote System Update via PCI Express*. i am facing issue when we trying to download any application

can anyone help me on this?

Steps Followed by me

Step. 1 : Load Mater_Image jic file through onboard blaster - Success

Step 2: Reboot the dvk - Success - Four LED glows

Step 3: Copy driver, Install & run the driver - Success

Step 4: download application - Facing issue(PFA)

#######################################################################################

Flash Device ID: 1021bb20

Step1 : Do you want to download the application image to FLASH?

(Please input 'y' or 'n' to select, and press ENTER to go on):y

Step2 : Please input start and end address of application image downloaded to FLASH.

(You could get below information from *.map file, and input here.)

(Warning: Please use start address 0x0 if you are downloading factory image!!!)

START ADDRESS :0x04000000

END ADDRESS :0x5568FFF

Step3 : PLease input program file directory.

(For example: /home/rsu_over_pcie/user/ru_auto.rpd)

/home/jetson/GRL_C2V/A10_Flash/vel_image/app2c_auto.rpd

Info : Download application image into Flash, file size is 22450176 Bytes, start address is 0x4000000

Erasing EPCQ flash ...

################################################## 100%

Writing EPCQ flash ...

################################################## 100%

Reading back data from Flash ...

Warning : Flash data error at addr 0xc000000, expected data is 0x3a, but read data is 0x0

Warning : Checking stop due to read back data error

Step4 : Do you want to reconfig FPGA?

(Please input 'y' or 'n' to select, and press ENTER to go on):

Note: I am able perform Step4 (reconfig) With initial configuration(loaded using onboard blaster). Yes, able to reconfig different application

@Ryan_M_Intel

Thanks for the example design.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thank you for contacting Intel community.

Per my understanding, you are using design example from below?

Also,

If your design is sensitive to the PCIe boot-up requirement, Intel recommends that you do not use the direct-to-application feature.

Intel recommends that you set a fixed start address and never update the start address during user mode. You should only overwrite an existing application configuration image when you have a new application image. This is to avoid the factory configuration image to be erased unintentionally every time you update the start address.

Can you try this? Let me know your feedback.

Regards,

Aiman

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

Thanks for your response.

Yes, I am using design example from below link

We are using same example design & driver.

"If your design is sensitive to the PCIe boot-up requirement, Intel recommends that you do not use the direct-to-application feature."

- can u please help how to disable direct-to-application feature?

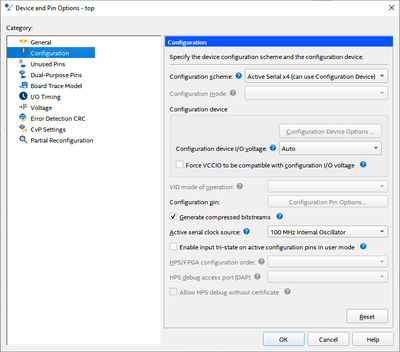

Note: Configuration Mode is disabled from tool

"Intel recommends that you set a fixed start address and never update the start address during user mode"

- Yes, we are not changing start address and trying to update only application image

"You should only overwrite an existing application configuration image when you have a new application image. This is to avoid the factory configuration image to be erased unintentionally every time you update the start address."

- We are using master image jic file and updated through onboard blaster.

- We try to replace the application image(either 1 or 2) by using same master image(ru_auto) rpd file.

We are getting read back data error error after 100% Erase & Write Completed

Flash Device ID: 1021bb20

Step1 : Do you want to download the application image to FLASH?

(Please input 'y' or 'n' to select, and press ENTER to go on):y

Step2 : Please input start and end address of application image downloaded to FLASH.

(You could get below information from *.map file, and input here.)

(Warning: Please use start address 0x0 if you are downloading factory image!!!)

START ADDRESS :0x04000000

END ADDRESS :0x5568FFF

Step3 : PLease input program file directory.

(For example: /home/rsu_over_pcie/user/ru_auto.rpd)

/home/jetson/GRL_C2V/A10_Flash/vel_image/app2c_auto.rpd

Info : Download application image into Flash, file size is 22450176 Bytes, start address is 0x4000000

Erasing EPCQ flash ...

################################################## 100%

Writing EPCQ flash ...

################################################## 100%

Reading back data from Flash ...

Warning : Flash data error at addr 0xc000000, expected data is 0x3a, but read data is 0x0

Warning : Checking stop due to read back data error

Step4 : Do you want to reconfig FPGA?

(Please input 'y' or 'n' to select, and press ENTER to go on):

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Apologize for my previous response, but I need some clarification below:

- When following the design example, is there any changes made in the design? If yes, which part?

- Is the design already programmed? It seems like it has but error at readback. If so, is the design functioning as intended?

Regards,

Aiman

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Greetings!

- When following the design example, is there any changes made in the design? If yes, which part?

- No change on design example. We are used same master_image - Is the design already programmed? It seems like it has but error at readback. If so, is the design functioning as intended?

- Write flash is completed. Readback error

- when we perform step 4(Do you want to reconfig FPGA?) with proper start address. its showing " Users Watchdog Timer timeout"

- The design not functioning as intended

Step4 : Do you want to reconfig FPGA?

(Please input 'y' or 'n' to select, and press ENTER to go on):y

(Warning: Please use start address 0x0 if you are reconfiguring to factory image!!!)

START ADDRESS :0x04000000

Info : Saving PCI control registers of the board.

-- Write 32bits 0 to bar 0, addr 2020004

-- Write 32bits 0 to bar 0, addr 2020008

-- Write 32bits 1 to bar 0, addr 2020010

-- Write 32bits 4000000 to bar 0, addr 202000c

-- Write 32bits 1 to bar 0, addr 2020018

Info : Restoring PCI control registers of the board.

-- Read 32bits ffffffff from bar 0, addr 2020000

Info : Altera Remote Update: Users Watchdog Timer timeout

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Can you try to test the design with the jic file first.

- Program the Flash with the jic file shipped with the design.

- Shut down the system and then power on again, observed four red LED lit on.

- Install the driver and run the application, select not to download the application image.

- Select reconfig the FPGA, use start address 0x2000000 or 0x4000000

If this is working, then the hardware is good for further testing.

Regards,

Aiman

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes,

As I mentioned in my first post I am able to swap the application through PCIe using driver and application which we downloaded through JTAG.

We are able to swap the application and factory image frequently without any issues.

We don't have issue with setup or hardware. Same setup used for PCIe based user projects

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

When checking with our internal team, we notice that your rpd file name does not match with the one shipped with our design example. Did you use the one shipped with our design?

Regards,

Aiman

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @NurAiman_M_Intel

Thanks for your response.

We have downloaded the project from below link(Design store )

https://fpgacloud.intel.com/devstore/platform/20.4.0/Pro/intel-arria-10-fpga-remote-system-update-via-pci-express/

arria10_pcie_rsu.par.

We extracted the project and using it.

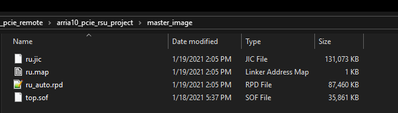

when we do that we got master image and its named like below image

We used same rpd file. Initially we tried with our own rpd file. Errors are same.

Below one is with master image (PFA for detailed log)

#################################################################################

# PCIe information: #

# Vendor ID 1172 #

# Device ID e001 #

# Operating at 8 GT/s with 4 lanes #

#################################################################################

#######################################################################################

#RSU Over PCIe Linux User Application #

#Operation steps: #

#Step1 : Select whether or not to download the application image into FLASH. #

#Step2 : Enter start and end address of application image to be downloaded into FLASH #

#Step3 : Enter the application image file directory #

#Step4 : Select whether or not to reconfigure the FPGA #

#Step5 : Enter start address of reconfiguration image in FLASH #

#######################################################################################

Flash Device ID: 1021bb20

Step1 : Do you want to download the application image to FLASH?

(Please input 'y' or 'n' to select, and press ENTER to go on):y

Step2 : Please input start and end address of application image downloaded to FLASH.

(You could get below information from *.map file, and input here.)

(Warning: Please use start address 0x0 if you are downloading factory image!!!)

START ADDRESS :0x04000000

END ADDRESS :0x05568FFF

Step3 : PLease input program file directory.

(For example: /home/rsu_over_pcie/user/ru_auto.rpd)

/home/jetson/GRL_C2V/A10_Flash/master_image/ru_auto.rpd

Info : Download application image into Flash, file size is 22450176 Bytes, start address is 0x4000000

Erasing EPCQ flash ...

################################################## 100%

Writing EPCQ flash ...

flash_controller_write offset_temp = 0x4000000 buf_offset = 0x0 burst_length = 0x10000

-------------------------------------------------- 0%flash_controller_write offset_temp = 0x4010000 buf_offset = 0x10000 burst_length = 0x10000

..

..

#################################################- 99%flash_controller_write offset_temp = 0x5560000 buf_offset = 0x1560000 burst_length = 0x9000

################################################## 100%

Reading back data from Flash ...

read_back_data_check file_size = 0x1569000 file_size_count = 0x1569000

read_back_data_check offset_temp = 0x4000000 buf_offset = 0x0 burst_length = 0x10000

Warning : Flash data error at addr 0xc000000, expected data is 0x3a, but read data is 0x0

Warning : Checking stop due to read back data error

Step4 : Do you want to reconfig FPGA?

(Please input 'y' or 'n' to select, and press ENTER to go on):

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I am checking this with my team. I will get back to you soon.

Regards,

Aiman

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

From your reply, this imply that the PCIe link is good, the master jic file is good, the path to trigger reconfig is working and the reconfig process completed without issue.

Did you refer to the ru.map file for the start address and end address when running the application? If no, please do.

Regards,

Aiman

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

@NurAiman_M_Intel

Yes, We are using Start Address and END Address as per ru.map file.

Page_0 0x00000020 0x01569FFF (0x0156958B)

Page_1 0x02000000 0x03568FFF (0x03568F27)

Page_2 0x04000000 0x05568FFF (0x05568F27)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

- I noticed from all your previuos reply, all the details were tested using Page_4 address.

Have you try to program Page_0 and Page 1? Are they success?

Page_0 0x00000020 0x01569FFF (0x0156958B)

Page_1 0x02000000 0x03568FFF (0x03568F27)

Page_2 0x04000000 0x05568FFF (0x05568F27)

2.On top of that, at step 4, did you press Y? If yes, did the FPGA able to boot up and work as intended?

Step4 : Do you want to reconfig FPGA?

(Please input 'y' or 'n' to select, and press ENTER to go on):

Regards,

Aiman

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

@NurAiman_M_Intel

1. Have you try to program Page_0 and Page 1? Are they success?

Yes, We try to program Page_0 and Page 1; its not success

2.On top of that, at step 4, did you press Y? If yes, did the FPGA able to boot up and work as intended?

No, When we program Page_0 or Page_1 or Page_2 through PCIe, FPGA did not boot up

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Can you please try again by following below:

[1] Erase the flash using Quartus Programmer.

[2] Restart the flow by generating the JIC file with image 0, image 1 and image 2 in it and then program it into the flash.

(Follow page 8 in the document)

[3] generate the rpd file for image 2, then try again to update the image using terminal

(follow page 18 - section 3.7.2)

Regards,

Aiman

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We do not receive any response from you to the previous reply that I have provided. This thread will be transitioned to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page