- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I must be doing something really stupid here.

The problem I have is that I seem to have a disagreement between instruction register values in TCL script and in Verilog.

In TCL:

set RESET_HI_CMD 11

set RESET_LO_CMD 12

..

device_virtual_ir_shift -instance_index 0 -ir_value $RESET_LO_CMD

setJTAGBypass

after 3000

device_virtual_ir_shift -instance_index 0 -ir_value $RESET_HI_CMD

setJTAGBypass

In Verilog:

localparam RESETHI = 4'b1011; // Definitely 11, same as TCL

localparam RESETLO = 4'b1100; // Definitely 12, same as TCL..

if( opco[3:0] == RESETLO)

begin

notReset <= 0;

oLED1 <= 0;

oLED8 <= ~ oLED8;

end

else

if( opco[3:0] == RESETHI)

begin

notReset <= 1;

oLED1 <= 1;

oLED7 <= ~ oLED7;

end

What I'm observing is a sequence of RESETHI-(3 seconds)-RESETLO on my device when it SHOULD be RESETLO-(3 seconds)-RESETHI

Any ideas please?

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, could you check if the ir command is correct by using the show_equivalent_device_ir_dr_shift argument.

If it is correct, it could be your design issue.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

@YuanLi_S_Intel is this what you would expect to see?

Info (262019): Equivalent device ir and dr shift commands

Info (262020): device_dr_shift -length 12 -dr_value 00B -value_in_hex

Info (262020): device_dr_shift -length 12 -dr_value 40C -value_in_hex

(3 second delay)

Info (262019): Equivalent device ir and dr shift commands

Info (262020): device_dr_shift -length 12 -dr_value 00B -value_in_hex

Info (262020): device_dr_shift -length 12 -dr_value 40B -value_in_hex

I'm assuming the 40C corresponds to my RESET_LO_CMD (12) and 40B corresponds to RESET_HI_CMD (11) ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

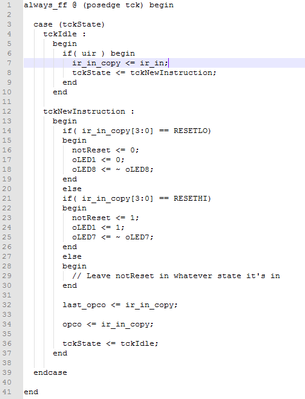

@YuanLi_S_Intel there must be something wrong with my design. I've been struggling with this for weeks now.

I expect to see LED8 toggle, followed by LED7 toggle (RESETLO, 3 seconds, RESETHI). But what I see is the opposite (LED7 toggle= RESETHI, 3 seconds, LED8 toggle=RESETLO)

Am I not using uir correctly?

The full project can be found here: https://github.com/SparkyNZ/FixReset

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

@YuanLi_S_Intel I hooked up the VJTAG pins to an external logic analyzer and I think I know what is wrong with the design.

My design assumed that the tck signal is a regular clock - but it isn't. It only oscillates when there is incoming data.

So.. my question is: What would be a typical frequency for tck when it is oscillating? I have a 2Mhz clock which I am using in my design - would this be too slow to service the tck/VJTAG signals??

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am glad it is solved now.

Meanwhile for the TCK frequency, it affects the speed of communication using JTAG. You may put higher frequency to increase the speed. However, too high will cause communication issue as well. You can try and find the optimum speed for your case.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page