- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

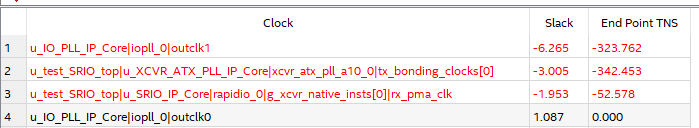

In my design there's a 5G 4X Rapid IO IP Core. A single TX PLL is instantiated to drive

tx_bonding_clock_ch0~3.

I've tried to drive the sysclk signal with txclk(output from the RapidIO IP Core) and a

250MHz clock(output from a IO_PLL IP Core), both of the two cases got negative setup slacks

after timing analysis, which result in error data in rapidio packet, as you can see in the

following screenshot.

The frequency of reference clock is 100MHz.

Any suggestions?

Thanks, regards.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks.

Can you give me an email address so I can send my design to you?

Regards.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hie,

Yes, please send your design to my email address nathan.ramachandran@intel.com

Anyway from your latest description, I am able to identify some incorrect clock connection information. syslck is the avalon sysclk. Connecting to tx_clk (which is sourced from transceiver PLL) is not recommended. Hence, please connect to IO PLL IP core. Also ensure the recommended frequency for sysclk is met. Currently you seem to be suing 250MHz which does not meet the maximum recommended frequency .Its documented in Table 16 of the RapidIO User Guide below:

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug_rapidio.pdf

Please update your clock connections following the user guide.

Regards,

Nathan

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page