- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

i have little experience in FPGA programming.

My situation: I am an intern and eight weeks ago i had a fpga in hand for the first time. I am using the Polmaddie 7 DevBoard with a cyclone 10.

My job is to sample a noisy digital signal, to check the quality of the signal. Its a simple serial interface with one startbit, seven databits and two stopbits. To messure the jitter i realized a statemachine with a high frequency clk, this is working.

But how can i scan the y-axis, to measure noise and overshoots?

On the board is no ADC installed and if possible , i would like to use no external. Is it possible to realize ADC programmatically (VHDL or AHDL), or is there a completely different way?

I am grateful for every tip.

Greet Ben

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

In short - you can't. FPGAs, on their own, don't (generally) had any ADC capability. MAX10 FPGAs do. However, depending on your signal - and particularly the scale of the noise on it - they're not likely to be sufficient to allow you to measure the noise.

Without some external circuitry or ADC you won't be able to determine an 'y-axis' behaviour beyond a logic high or low.

Cheers,

Alex

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

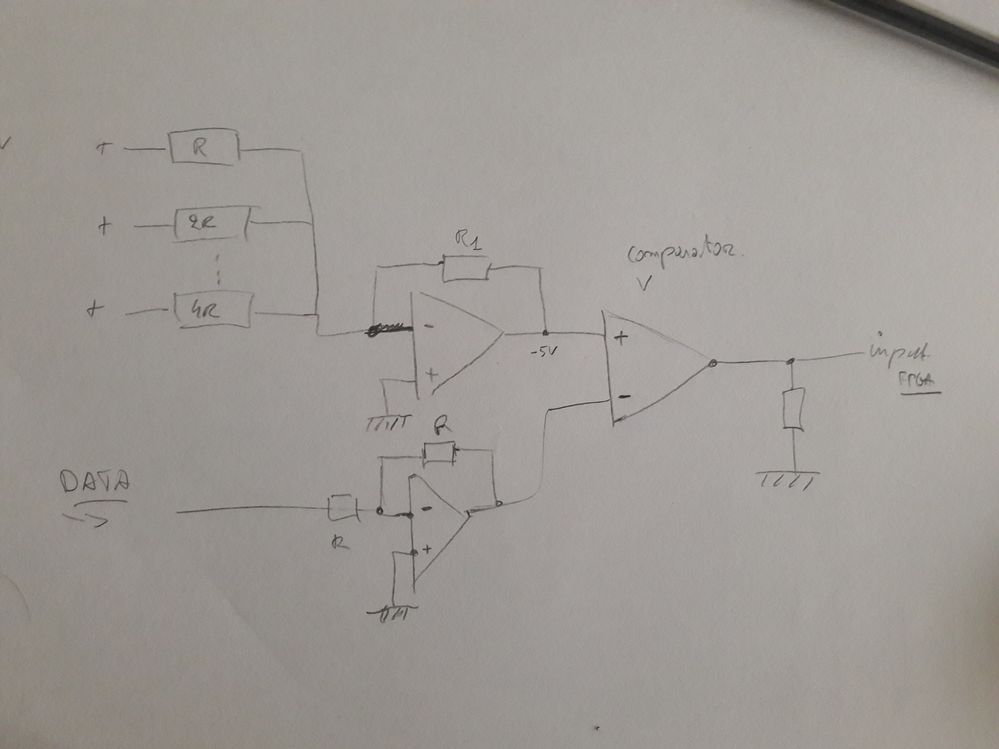

That's not entirely true. There's a (quite dirty) way by abusing the differential inputs of the FPGA. Make a resistor-ladder to generate all compare-steps, tie these to the negative input of N differential inputs. Tie all positive inputs together and feed the analogue signal into the FPGA. This is probably the cheapest flash-ADC you can build these days, but it eats up quite a few IOs, which are always scarce (at least in my designs). If you don't need too many bits of resolution, it's worth a try.

I have no personal experience with this approach, but seen it a few times on other designs. I think it's worth a try it for a resolution of 4-5 bits max.

greetings from Germany,

Jens

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks Alex, danke Jens!

@JScho6

I already heard about it. My Problem is, nobody can tell me how bad the signal errors actually are. So first, I try a little more resolution with an external.

I am curretly writing another state machine, to write my data at the right time in a shift register and from there i can continue processing. I was doing similar with the timing/counter data before and therefore I used the ".shiftout" function from the "LPM_SHIFTREG" file to send the data back to my computer.

This time, I want to embed the "ADC_Controller" file, but Quartus complains, that this file can not be found and I can not open the PDF that Altera has online. Does anyone know if Intel / Altera has done anything?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I don't know what PDF you're referring to - it's always helpful to give us a title/link to help us. Many links have broken as a result of the Intel takeover.

I assume the 'ADC_controller' is an rtl file (VHDL/Verilog) that you've written. Right? You'll need to add it to your project. 'Project' -> 'Add/Remove files in project'...

Cheers,

Alex

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You can also build a DAC with your FPGA outputs using a few opamps and an use additional opamp as a comparator that compares the output of the improvised DAC with the signal you want to monitor. One digital input of your FPGA checks whether the DAC output value is below or above your signal. You start the measurement cycle with your DAC at Vref/2 then see if you are above for below Vref/2 and then proceed with Vref/4 or 3Vref/4 etc. In fact some ADC work like this internally. On the other hand, you might consider using an LTC1863 that does the job for you. (A good ADC does sample & hold like it is ment to be done, my proposal does not.)

Best Regards,

Johi.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page