- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

what you have changed in QSYS?

- Check the connections for Nios2 data- and instruction master ports.

- Check the connections of JTAG UART.

- Does Reset and Clock is working well?

- Check the BSP path in SBT

- try the "Run->Debug Configuratuions" tool in SBT

- use the "Hello World" example program in onchip RAM as simple test

Jens

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

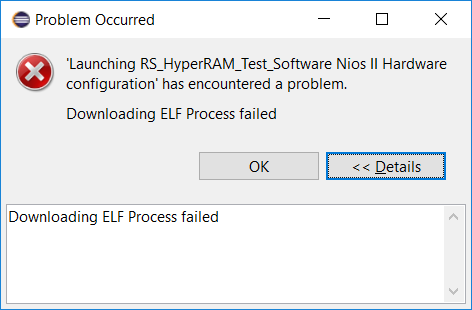

Thank you for your response. To be more specific, what happens is that I have completely generated the bsp, compiled the software, made the target and recompiled the FPGA. I then program the FPGA and the NIOS2 program runs as witnessed by the USER LEDs flashing. This implies to me that all is well with the Qsys system and the NIOS2. Then for some reason the first time that I try to debug the firmware in the SBT, I get an error that says that the BSP needs to be regenerated which I do. Then the second time that I try to debug the firmware I get the error message in the "Console" that says "Resetting and pausing target processor: FAILED, Leaving target processor paused". I also get a pop-up Error message box that says "Exception occurred during launch Reason: Downloading ELF Process failed". I have checked the "Ignore Timestamp and System ID" boxes in the Run Configuration. I have no idea why I can't debug this firmware that is obviously running upon initial download from the *.sof file. Can you help me figure out what the problem is?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

It seems to me that on the board another system is running than you want to debug. (Are the LEDs connected to Nios2? So clock and reset work)

Check in the Nios2 IDE the BSP project location in the Nios2 application project properties.

How do you create the bin files for FPGA configuration and Nios2 program and where are they stored on the board? Is it possible that you have programmed a different version?

Jens

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you all for your responses. I have tracked down the problem to the fact that I was using a copy of a Qsys system that was derived from a "Time Limited IP" Qsys system. I had removed the IP and renamed the Qsys, but there must have still been something in the Qsys that was causing the problem. I started from scratch and build a Qsys with the same features as Qsys that I had created by removing the "Time Limited IP" and it works like it should. However, it would have been nice to have a little more information about the problem than just the generic message "Downloading ELF process Failed".

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page