- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

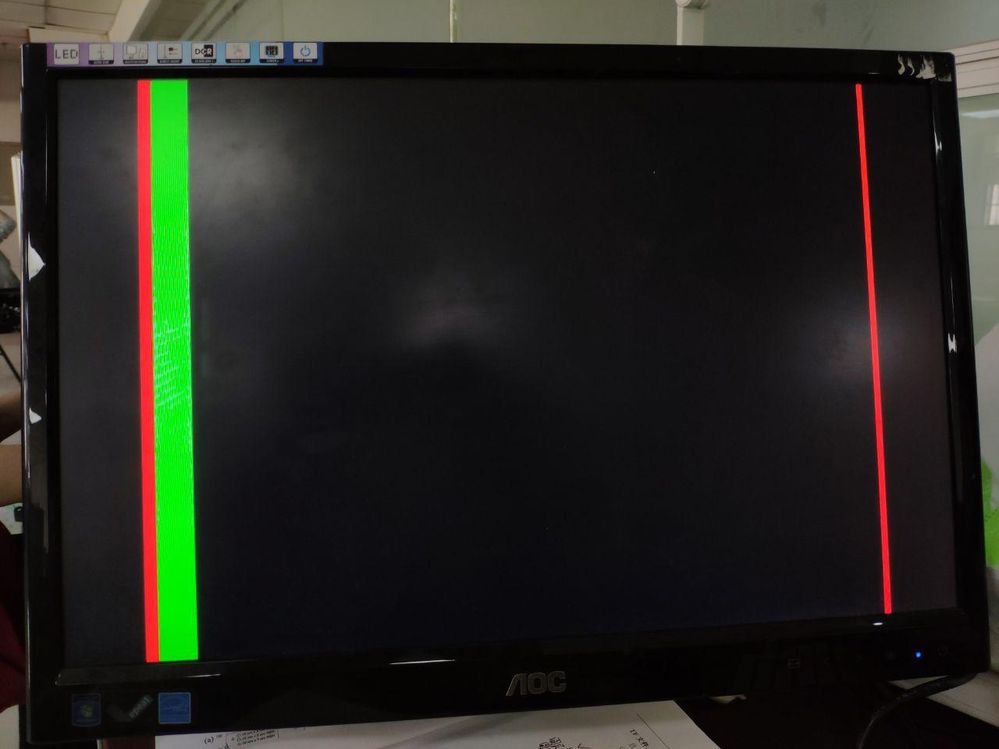

I wrote a short verilog code to test VGA display. Vga display needs red, blue, green, vscan and hscan signal. And DE1SOC use another DAC to convert red, blue, green digital signals to analog signals. DAC needs dac_clock, scan_n and blank_n signals.

The code is shown below. I use a pll to convert clk_50m to clk_25m and clk_100m. Clk_50m is originate from the clock in board.

module vgatest(

input wire clk_50m,

input wire rst_n,

output reg [7:0] red,

output reg [7:0] green,

output reg [7:0] blue,

output wire hsync,

output wire vsync,

output wire dac_clk,

output wire dac_sync,

output wire dac_blank

);

//-------------------------------------------------//

// 640*480 60Hz VGA

//-------------------------------------------------//

/*

back porch 48 33

sync pulse 96 2

front porch 16 10

*/

parameter H_SYNC_END = 96;

parameter V_SYNC_END = 2;

parameter H_SYNC_TOTAL = 800;

parameter V_SYNC_TOTAL = 525;

parameter H_SHOW_START = 10'd144;

parameter V_SHOW_START = 10'd35;

integer i,j;

reg [9:0] x_cnt;//0~800,96+48=144~640~16

reg [9:0] y_cnt;//0~525,2+33=35~480~10

wire [9:0] x_pos;

wire [9:0] y_pos;

wire [5:0] x_mo;

wire [5:0] y_mo;

wire [3:0] x_remainder;

wire [3:0] y_remainder;

wire clk_25m;

wire clk_100m;

wire clk_200m;

reg [3:0] direction_reg;

reg [7:0] red_reg;

reg [7:0] green_reg;

reg [7:0] blue_reg;

assign x_pos =(x_cnt <=10'd783 && x_cnt>=H_SHOW_START)?(x_cnt - H_SHOW_START) :10'd0 ;////0~639

assign y_pos =(y_cnt <=10'd514 && y_cnt>=V_SHOW_START)?(y_cnt - V_SHOW_START):9'd0;////0~399

assign x_mo=x_pos%10;//0~63

assign y_mo=y_pos%10;//0~39

assign x_remainder=x_pos/10;//0~9

assign y_remainder=y_pos/10;//0~9

pll_clock M1(

.refclk(clk_50m), // refclk.clk

.rst(~rst_n), // reset.reset

.outclk_0(clk_25m), // outclk0.clk

.outclk_1(clk_100m), // outclk1.clk

.outclk_2(clk_200m)

);

assign dac_clk=clk_100m;

assign dac_sync= 1'b0;

assign dac_blank = 1'b1;

//horizontal scan

always@(posedge clk_25m or negedge rst_n)

if(~rst_n) x_cnt <= 10'd0;

else if (x_cnt == (H_SYNC_TOTAL-1)) x_cnt <= 10'd0;

else x_cnt <= x_cnt + 1'b1;

//vertical scan

always@(posedge clk_25m or negedge rst_n)

if(~rst_n) y_cnt <= 10'd0;

else if (y_cnt == (V_SYNC_TOTAL-1)) y_cnt <= 10'd0;

else if (x_cnt == (H_SYNC_TOTAL-1)) y_cnt <= y_cnt + 1'b1;

//H_SYNC signal

assign hsync=(x_cnt<H_SYNC_END)?1'b0:1'b1;

//V_SYNC signal

assign vsync=(y_cnt<V_SYNC_END)?1'b0:1'b1;

always@(posedge clk_25m, negedge rst_n)

begin

// red={8{1'b1}};

if(~rst_n)

begin

red=8'b0;

green=8'b0;

blue=8'b0;

end

else if (x_pos>=10'd1 && x_pos<=10'd10)

begin

red<= 8'b11111111;

green<= 8'b0;

blue<= 8'b0;

end

else if (x_pos>=10'd10 && x_pos<=10'd40)

begin

red<= 8'b0;

green<= {8{1'b1}};

blue<= 8'b0;

end

else if (x_pos>=10'd635 && x_pos<=10'd639)

begin

red<= 8'b11111111;

green<= 8'b0;

blue<= 8'b0;

end

else

begin

red=8'b0;

green=8'b0;

blue=8'b11111111;

end

end

endmoduleThe monitor is almosts black. In line 120, I make the default color be blue rather than black. That is my first confusion.

When I change the line 97 from

else if (x_pos>=10'd1 && x_pos<=10'd10)to

else if (x_pos>=10'd0 && x_pos<=10'd10)The result confuse me again.

Blue part is shown correctly, but the red part is missing.

I tried to solve this problem these days, but I don't know why. Now that the monitor display vga signal, I believe vscan and hscan is correct. The problem may among r,g,b signal. I really don't know the reason.

- Tags:

- de1-soc

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I try to search vga example for DE1SOC, but I cannot find it. Most of example for DE1SOC is related to OPENCL, using c/c++ rather than verilog.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page