- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

We use 10CL055YU484C8G.

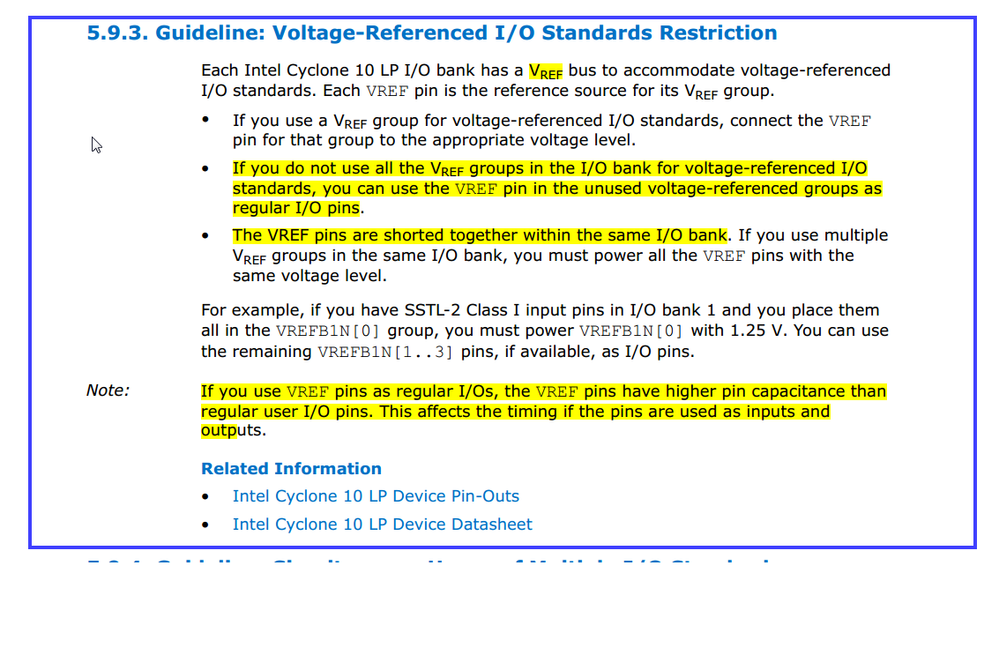

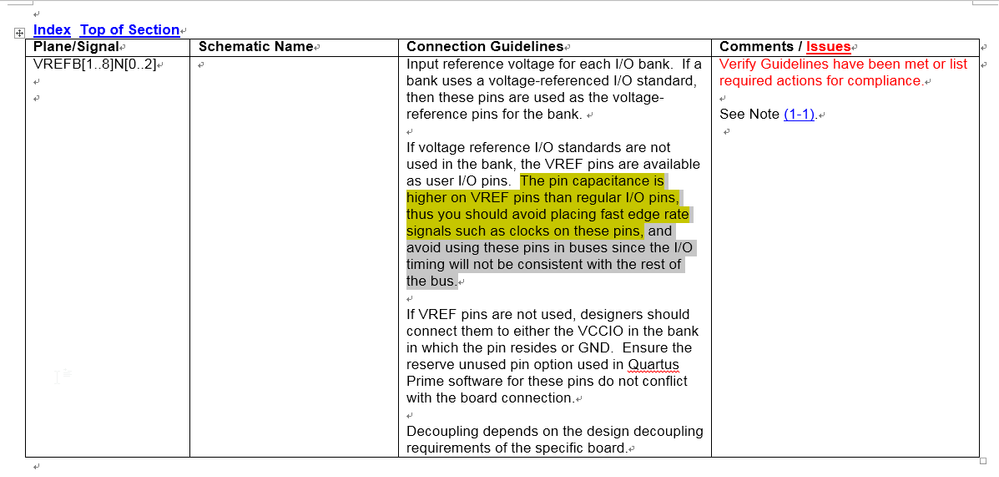

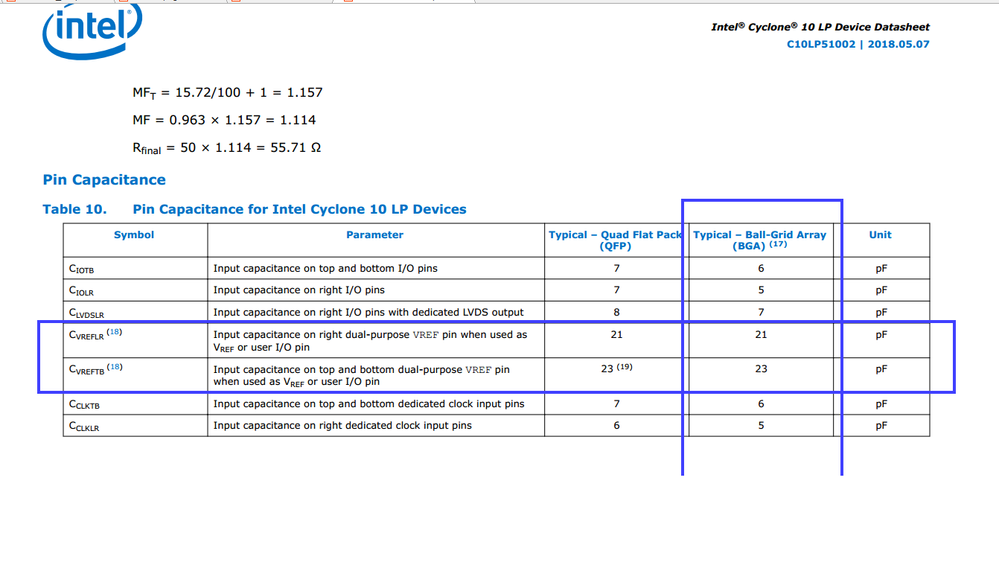

In Intel's 《cyclone_10_lp_schematic_review_worksheet.doc》 and Cyclone 10 LP Core Fabrice and General Purpose I/O Handbook, section 5.9.3, it mentioned "the VREF pins have higher pin capacitance than regular user I/O pins. This affects the timing if the pins are used as inputs and outputs" . Which means it might NOT able for VREF pins to input/output High speed signals.

Questions:

(1) We use VREF pins as regular IO. How can we quantitatively evaluate its speed? Can we use it to output 200MHZ IO signals?

(2) Same question for RUP and RDN pins used as user IO with 200MHZ speed.

Thanks!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We gave up on this topic. Managed to avoid using these VREF pins and RUP and RDN pins.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

up

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

up

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

up

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

upppppppp

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi ,

For the Vref Pins to get exact values, is it possible for you to simulate.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We gave up on this topic. Managed to avoid using these VREF pins and RUP and RDN pins.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page