- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

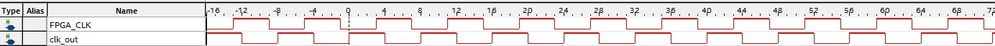

The device is Arria 10. IOPLL input clk freq is 100M,output0 is 100M and output1 is 800M. Output0 is used as an internal clock. In the image,this is the SignalTap screenshot,and sampling clock is ouput1(800M),Why the two signals are not aligned?

Link Copied

1 Reply

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi ,

Kinldy check, is there any phase sift is provided in the PLL IP. Mostly this will happens because of phase shift.

Regards,

Rs

Reply

Topic Options

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page