- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The following things are to be stored inside the FPGA:

1. Build date

2. Build time

3. Build top level file name

4. Build repository commit number for version controlled design

5. Submodule repository commit number for version controlled design

Is there a standard way to store and retrieve this information? The simplest method would be to somehow use JTAG to read them out.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi gyuunyuu,

Thank you for contacting Intel community.

For your information, 1. Build date, 2. Build time, can be obtained from the device itself. Please see the link below for the format,

https://www.intel.com/content/www/us/en/programmable/support/quality-and-reliability/decoder.html

Moreover, please clarify more about number 3, 4, 5 in order for us to help you with the queries.

Additionally, JTAG can only read device OPN and Chip Unit ID.

Regards,

Aim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Sorry, by build I meant the date and time of when the project was compiled. The item 3 is the ASCII name of the top level entity. The items 4 and 5 are related with Git based revision control system where we have hash number for the where we are on a branch in a repository.

Since customers would like to do this quite often, I would expect that Intel/Altera has created a method to achieve this which is supported by them?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi gyuunyuu,

We are sorry to tell you that we do not have the information to support your request. But for the record, we will raised this issue to our internal team for future support. We apologize for any inconveniences that come from us. Appreciate much for your understanding.

Regards,

Aim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

OK, I will ask an alternate question. I have tcl script that can execute and generate those values into a HDL file just before synthesis takes place. I just want to know what command has to be run from tcl to cause the Qsys system to generate again. If I am using shell , I can use the "qsys-generate".

What if I want to update the HDL file of a custom Qsys component via a tcl script, just before synthesis and then cause the Qsys system to regenerate just before synthesis starts? The "qsys-generate" can be run from shell but what do I need to use from the tcl script?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

You may execute the TCL script (let say first.tcl) that is use to update the HDL file of the custom Qsys component before synthesis by adding the command in the .qsf.

set_global_assignment -name PRE_FLOW_SCRIPT_FILE quartus_sh:first.tcl

For further information, you may refer to https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug-qpp-scripting.pdf (Chapter 1.9 Automating Script Execution)

You can either add the qsys-generate command in the first.tcl and add the above command in the .qsf file

or

create a .tcl that list all the execution flow in sequence and run the tcl.

Please let me know if you have any questions.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have 2 questions

1. qsys-generate is an executable and not a tcl command. What is the preferred way of executing the qsys generation from tcl script (in contrast to command line shell script)?

2. Is Quartus supposed to automatically regenerate the Qsys system for which it has a .qip file when we compile design, or it is the sole responsibility of the user to do this manually?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Q1: You may use the following to run the TCL script.

quartus_sh -t first.tcl

Q2: Yes. The software will regenerate the Qsys system if you add the .qsys file in the project.

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

YY, do I understand correct that there is no command within tcl in Quartus that carries out Qsys generation?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

qsys-generate is the TCL command that is used to generate the Qsys system. The software will regenerate the system even if you did not specify the command, provided you have added the .qsys file (not .qip) in the project.

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

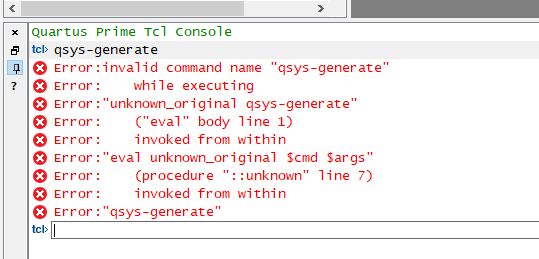

Executing the qsys-generate from tcl produces error as shown in the screenshot. Do I need to load some tcl package to make this work?

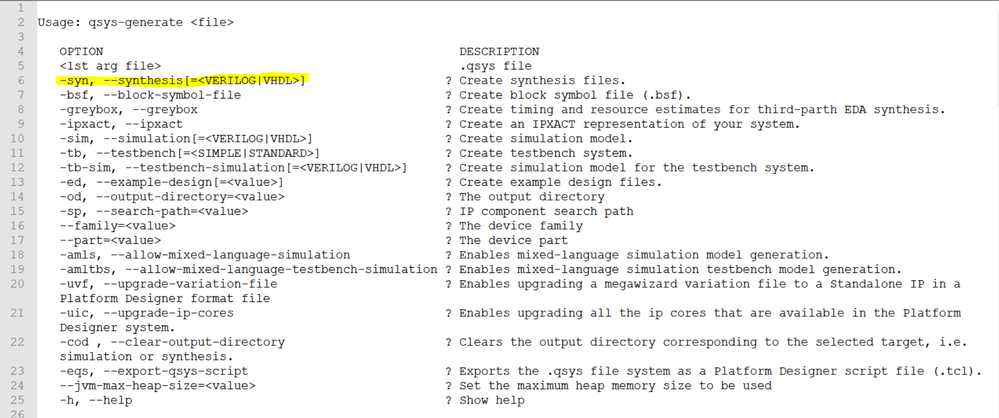

Including the .qsys into the Quartus project file seems to generate a system where everything is in verilog and it seems to clash with some other files that already exist with those names. If I include the .qsys file, how do I specify that when Quartus generates this system, it should be via VHDL files. There must be some global assignment that can be put into the .qip file.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

You have to execute the qsys-generate in the command line terminal instead of the TCL Console in the Intel Quartus Prime software.

You may specify the language when you execute this command. Attached is the help for your reference

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

May I know if you have any updates?

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I wrote a custom tcl script that generates a VHDL file with the compilation data and time, and the git hash values. This package is included into a register bank in the design. The register bank already exists and stores many different type of data used by the design. The register bank code is all in VHDL.

The compilation data and time, and the git hash values for the repositories that form the project can be read by using system console.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The project is now being compiled using a script based flow. It shall generate the Qsys system before synthesis. I did include the .qsys file into the design so Quartus automatically generates the Qsys system. However, I noticed that it (automatically) generates verilog synthesis files rather than VHDL files. It is not clear how to specify Quartus to automatically generate VHDL synthesis files instead when .qsys file is included into the project.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

You may go to Assignments > Settings > IP Generation HDL preference, set to VHDL

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Do you have any updates?

Thanks.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page