- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am trying to read from MAX10's UFM but the device does not assert the readdatavalid signal as specified in UFM user guide. Any guess why is it so? I am sharing the relevant code below:

task data_read_top;

case (read_state)

FLASH_READ_IDLE :

begin

read_state <= FLASH_READ1;

end

FLASH_PRE_READ :

begin

if (avmm_data_waitrequest)

read_state <= FLASH_PRE_READ;

else

read_state <= FLASH_READ1;

end

FLASH_READ1 :

begin

data_read1(00000_0101_1111_0000);

read_state <= FLASH_READ2;

end

FLASH_READ2 :

begin

data_read2;

read_state <= FLASH_READ3;

end

FLASH_READ3 :

begin

if (~avmm_data_readdatavalid)

begin

read_state <= FLASH_READ3;

end

else

begin

data_read3;

data_out <= avmm_data_readdata;

read_state <= FLASH_READ4;

end

end

FLASH_READ4 :

begin

read_state <= FLASH_READ_IDLE;

end

default :

read_state <= FLASH_READ_IDLE;

endcase

endtask

task data_read1;

input [16:0] addr;

begin

avmm_csr_read <= 1'b0;

avmm_csr_write <= 1'b0;

avmm_csr_addr <= 1'b0;

avmm_data_addr <= addr;

avmm_data_read <= 1'b1;

avmm_data_burstcount <= 2'b01;

end

endtask

task data_read2;

begin

avmm_csr_read <= 1'b0;

avmm_csr_write <= 1'b0;

avmm_csr_addr <= 1'b0;

avmm_data_read <= 1'b0;

avmm_data_addr <= 17'b0000_0000_0000_0000_0;

avmm_data_burstcount <= 2'b00;

end

endtask

task data_read3;

begin

avmm_csr_read <= 1'b0;

avmm_csr_write <= 1'b0;

avmm_csr_addr <= 1'b0;

end

endtaskThe task data_read_top itself is called in another case statement. What I have observed in SignalTap II is that it remains stuck at state FLASH_READ3.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Not able to understand the state machine can you post full code?

Have you checked your logic using modelsim?

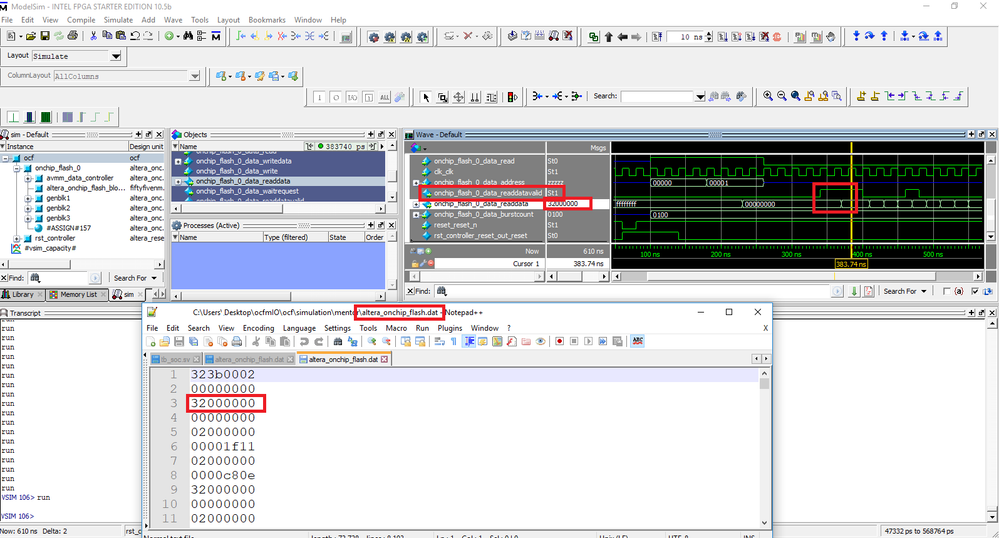

I can simulate the Flash IP, it works fine. Attached the image.

So for debugging check your logic using modelsim first.

Regards

ARS

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for the reply. My code is attached. Actually I tried simulating the design first but Modelsim gives these errors:

- Instantiation of 'altera_onchip_flash_avmm_data_controller' failed. The design unit was not found.

- Instantiation of 'fiftyfivenm_unvm' failed. The design unit was not found.

which I am unable to resolve, so moved directly to post synthesis verification.

Another thing that I have observed is if I remove the wait condition for 'readdatavalid' signal, it gets asserted by the UFM core and data is shared on the data bus but is mismatched from the address.

Besides can you explain, that you sent a read request for data to be read from 17'h00000 and 17'h00001 but it seems that UFM read some different data.

Regards

Sarmad

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Please Reply,

We are facing the same error. Its on priority.

Best regards

Shweta Sawant

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page