- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I am using the 10M16SAE144 with dual compressed images, but regadless of the state of the CONFIG_SEL pin, config is done all the time from CFM1. Both images are valid. I had changed the images vice versa, but configuration is always done from CFM1.

Settings:

Internal Configuration, enable CONFIG_SEL Pin

not checked configure device from CFM0 only

not checked use second- image ISP as default setting if av.

Contents of the .map file:

BLOCK START ADDRESS END ADDRESS

ICB 0x00000000 0x00000FFF

UFM 0x00001000 0x00008FFF

CFM0 0x0004B000 0x0008CFFF (0x0006D643)

CFM1 0x00009000 0x0004AFFF (0x0002B82F)

Max 10 Setting:

EPOF: OFF

Verify protect: OFF

Watchdog value: Not activated

Configure device from CFM0 only: OFF

POR: Instant ON

IO Pullup: ON

SPI IO Pullup: ON

I wonder at the fact that the addr of CFM1 is lower than the addr of CFM0.

Any idea what is going wrong?

Thank you.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi MShafiq,

Thanks for your answer.

I use the HW-pin of the device with a jumper (with 10k pull down resistor / 1k pull up resistor). The logic level change is ok (0.1V / 3.0V). Already changed the device, it is the same.

Best regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

1) using the software method can not be done fast, because there is no processor inside the design and therefore I had to write some HDL code for using the avalon bus of the dual config ip.

2) I have made the measurement. Yes, there is a problem, because the value of the pull-down resistor (as stated in the document) of 10k is to large, 2k2 or less should be used. Changing this, shows a voltage level of 0.4V or less during power on.

But unfortunately this will not change the behaviour always booting the CFM1.

3) I have created two different .sof files with diff. names. Both are valid and when written in the CFM1 they work correct.

4) In the pin-out file one can see:

~ALTERA_CONFIG_SEL~ / RESERVED_INPUT : 126 : input : 3.3-V LVCMOS : : 8 : N

which show to me that the Config-sel-pin is an input.

Remember that there is only a passive 2k2 resistor to ground connected to this pin.

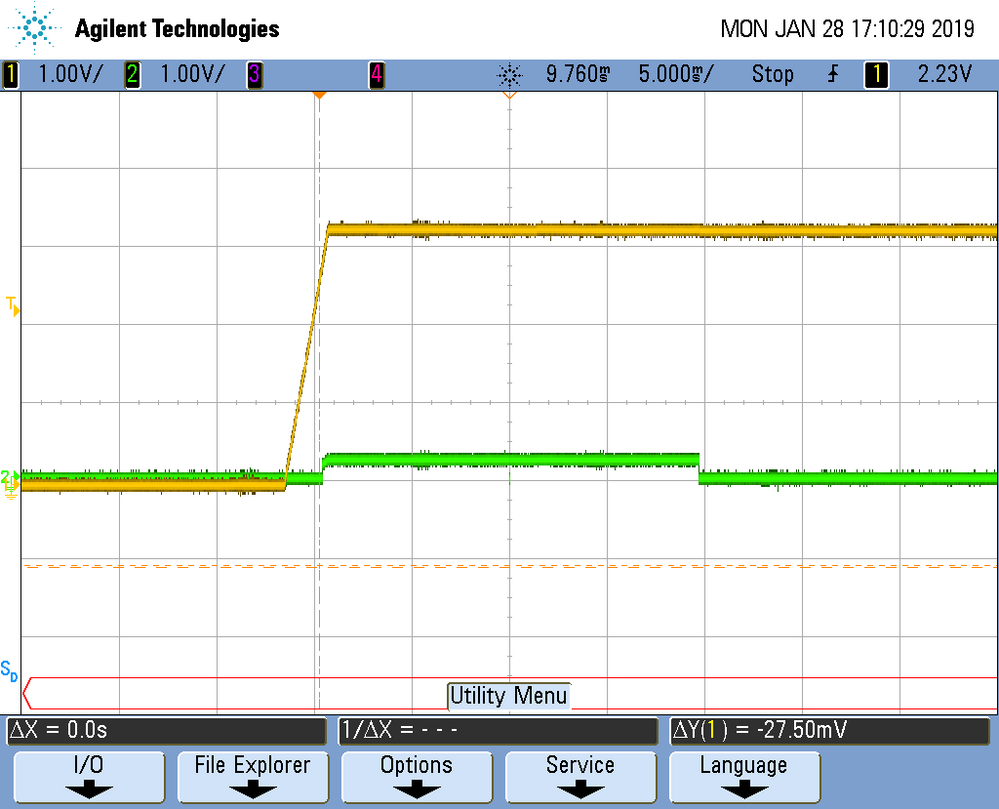

Why I can see a 20us low puls aprox. 10ms after PON, and why the pin goes to 0V aprox. 20ms after PON?

Can this be a reason for the problem?

Thanks for help.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page