- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Experts,

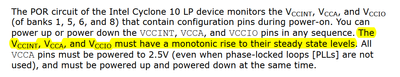

I am using the LDO for Cyclone 10LP power supply, but the none-monotonous power rise is found during the power up on my board as below figure shown. This may be caused by high inrush current to power supply.

My question is:

1. Will the none-monotonous power rise cause Cyclone10LP chip damaged? or impact the chip reliability?

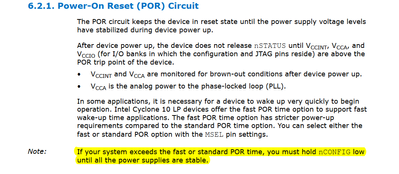

2. if the NCONFIG pin is hold to low till all the power supplies are stable, can this be a workaround for this non-monotonous issue? I found some related note in the handbook as below, but not sure if it can be used for my case.

Thanks & Best Regards,

Shawn

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I found a forum posts related to the topic.

Non-monotonic rise on the power supply - Intel Community

The datasheet has the following statement "All supplies must be strictly monotonic without plateaus." This is specifically applicable to all VCC voltages.

Please check the recommendations at the footnote below Table 3 of the datasheet.

Regards.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Hope the query is answered. Closing the case.

Thanks.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page