Hi everyone !

Firstly, I hope that you are having a good day. In a second time,

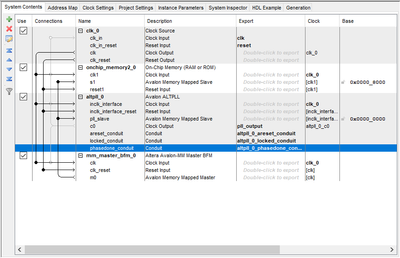

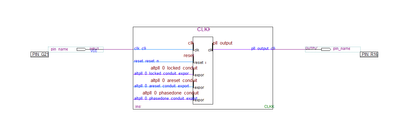

I have a DE0 board from Altera and I want to display on an oscilloscope a clock signal from a pin output on the board's expansion header (it's the PIN R16 I think). The output clock have to be a multiplication of the input frequency by using a PLL and the input signal would be coming from the board's oscillator crystal with a frequency of 20 MHz. For this, I'm using Qsys from QuartusII Web Edition. I wanted to know if these component are sufficient to accomplish my project. I want to know too if the locked, areset and phasedone conduit are necessary for the project and if it's the case how to connect them. And to finish, if the Avalon_MM_Master is really useful here.

here's the picture of my model :

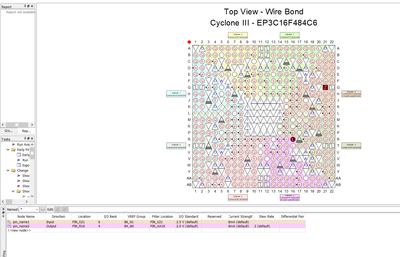

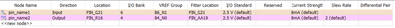

and the picture of my pin planner :

and the zoomed version :

and the picture of my .bdf where we can see that I don't know how to connect all the exported conduit

thanks in advance for the replies,

Best regards

I believe the community have answered your inquiries, do you need further help in regards to this case?

連結已複製

You don't need locked, areset and phasedone conduit signals. You don't need on chip memory and avalon master either. You just need basic pll with your configuration. Connect clock in signal to pll and export the pll output signal and connect it in pin planner. Don't forget entering the input clock's frequency and set the pll frequencies correctly.

The things you have done seem to be ok but you didn't upload the port mappings in code. If you don't connect the pll's output to the entity's output signal it doesn't work.

thanks for your reply ! So I need to add a .vhd file where I have to inform the port map ? Or I have to use the HDL file that have been generated by quartus II ?

OP is using a schematic instead of HDL code, so what you mention about the output connection is handled there.

This should work fine.

With that, I will now transition this thread to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you.

Best Regards,

Richard Tan

p/s: If any answer from the community or Intel support are helpful, please feel free to give Kudos and select the best solution.