- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I am using quartus to program a Stratix10 board. The board version is 1sg280hu2f50e2vgs1@1.

After programming the bitfile we are getting an error message in quartus pgm with log:

31:Error (18952): Error status: The device chain in Programmer does not match physical device chain. Expected JTAG ID code 0x032250DD for device 1, but found JTAG ID code 0x020A40DD.

32:Error (209012): Operation failed

34:Error: Quartus Prime Programmer was unsuccessful. 2 errors, 1 warning

35: Error: Peak virtual memory: 2480 megabytes

36: Error: Processing ended: Mon Nov 2 12:10:40 2020

37: Error: Elapsed time: 00:00:11

38: Error: System process ID: 23316

The quartus version used for this run was :

Info: Running Quartus Prime Programmer

Info: Version 19.4.0 Build 64 12/04/2019 SC Pro Edition

We have been stuck with this error and have tried to look up intel solutions to no avail. Can you please help us find the issue.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

May i know which bistream file is used for programming? Based on the error message, it seems like the device number selected in the bitstream is not the same as the device using on the board.

Thank You.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello, YuanLi has pointed to what is wrong, just to point to what can be wrong:

JTAG ID code 0x020A40DD belong to ARRIA II GX EP2AGX125EF29C5

Expected code was 0x032250DD belonging to on Board Stratix 10 GX

Check project device property update device and run again sintesys and planning too.

If a POF or SOF prebuilt file was chosen, then select the correct one for that board.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I tried changing the version of the device from Engineering Sample board to normal but it still errors out with the same issue.

Does this have to do anything with the MSEL pins on the board?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

MSEL is matter depending on the configuration scheme you are using? Tell me, which bitstream you are programming? Is it SOF, POF or JIC?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am using a SOF file to program the board.

This is the output of my jtagconfig command on the board:

/remote/sbg_toolkits/Altera/quartus_19_4_pro_linux/quartus/bin/jtagconfig

1) USB-BlasterII [1-2.3]

020A40DD 5M(1270ZF324|2210Z)/EPM2210

C32250DD 1SG280HH1(.|S3|AS)/1SG280HH2/..

Is the 020A40DD Jtag ID correct for the Stratix10 GX board?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

- MSEL has nothing to do with issue.

- MSEL Select, if multi image design is the case, which one has to boot from.

From your post Device id on board is detected and is different from one on programming file you choose for programming.

I see you are using Linux, this is better choice but has some caveat need be addressed for. Are required library ok? Try launch by shell and look to what happen on terminal.

Chekup also AN807 about board setup, some dip switch on page 7(not MSEL) appear as selected for JTAG CPLD update.

Last question again NO : Stratix 10 is on board and detected by JTAG as from previous answer->

JTAG ID code 0x020A40DD belong to ARRIA II GX EP2AGX125EF29C5 (WRONG)

Expected code was 0x032250DD belonging to on Board Stratix 10 GX (Right one(expected for on board device))

https://bsdl.info/details.htm?sid=c1b9a05b8b8b08b888ca59b002289d77

The error you report appear as programming file not prepared for stratix board.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Please partially disregard some detail on previous reply:

About last question, I seen late two device appear on jtag chain, is the right one selected?

Stratix is the device 2 not the device 1.

So you assigned stratix file to CPLD EPM2210 or to Stratix? can you post a screenshot of programmer in actual config

and then after pressing auto detect button?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

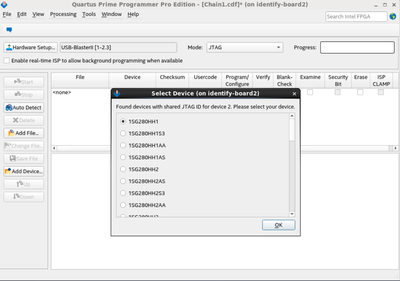

When I bring up the programmer this is what I see:

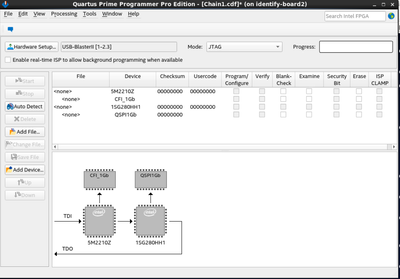

And if I select HH1 device here is the chain:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello, exactly as from jtagd stratix device is chained as device 2, right one on my previous post must sound as correct one.

On graphic programmer view sound as "right side <-(one)" you are trying program the left device with file built for stratix.

I don't own this board but looking inside manual instruct use command line programmer directing file to device 1 (Left on graphic version). This seem wrong and generate the error you experienced.

Double click on right IC image and add file or click on file relative to Stratix, leave CPLD 2210 unselected.

If you are using command line, board manual use device 1 in chain but on your board this is CPLD not stratix.

Try change chain device from 1 to 2 and retry.

And last but not least, never seen as reply, which file are you using for?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I reconnected my previous Stratix10 board which has power issues and was able to notice that the JTAG ID code is different.

The board that I am trying to debug in this thread has the info:

Info (213045): Using programming cable "USB-BlasterII [1-2.3]"

1) USB-BlasterII [1-2.3]

020A40DD 5M(1270ZF324|2210Z)/EPM2210

C32250DD 1SG280HH1(.|S3|AS)/1SG280HH2/..

V/S the old board which has the info:

Info (213045): Using programming cable "USB-BlasterII [1-2.3]"

1) USB-BlasterII [1-2.3]

032250DD 1SG280HH(1S1|2S1|3S1)/..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I was able to target the board with JTAG ID CODE C32250DD.

The Stratix10 Part number used for this is:

1SG280HNF43 with JTAG ID CODE :

0xC32250DD

Can you please point me to the PIN assignment for the OSC_CLK (FPGA clock) on board.

Regards,

Prateik

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Just would like to check, which bitstream are you using to programming stratix device? I would recommend you to delete the 2 devices on programmer, then add the bitstream that you want to program into the programmer and then program it. Also, you will need to change the TCK frequency to 6MHz.

Thank You.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Do you mean the location of OSC_CLK_1 on the board?

You may find it on the board schematic available at link below:

Also for your information. This thread will is already transitioned to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you.

Regards,

Bruce

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Yes the osc_clk_1. I have tried the BA22 pin as per your schematic link, but my design still shows X's on the data bus. Can I use chipscope in quartus to verify the pin for sample clock?

We have a feeling the sample clock is not driving the design.

Also, do you have an example design for this particular board:

1SG280HNF43 with JTAG ID CODE :

0xC32250DD

It would be easier to replicate our design based off of an example design for this part number of the S10 GX board.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page