- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

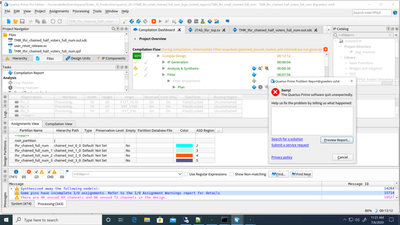

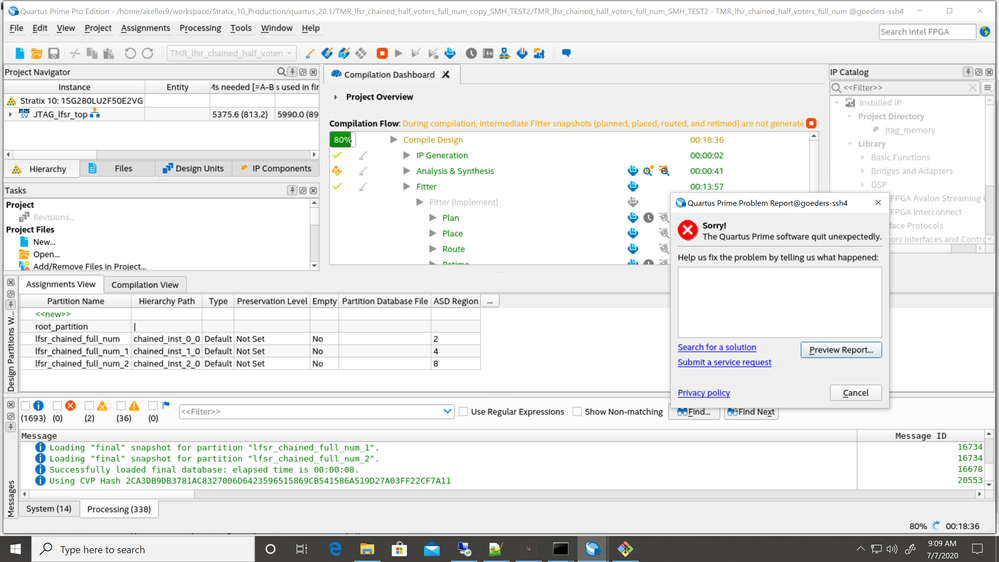

I am making several designs on the stratix 10 (1sg280LU2F50E2vg). I have found that if I declare more than 4 partitions as ASD regions than it will crash with an unexpected error during the assembler. As long as I have declared 4 or less regions it generates fine. I have tried this on several different designs and they all behave the same. 4 regions is below documentation specs in the SEU mitigation guide am I somehow messing up the declarations or missing a setting somewhere?

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

May i know how do you declare the ASD region? Have you included .smh file? Also, can you try 1,2,4,8 instead?

Thank You

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am opening the design partition window (as you can see in the screen shot) and then declaring the ASD region by putting in an assigned number in the ASD region column. I tried it with 2,4,8 and it didn't work. I retried with 1,2,4,8 and it didnt work. In documentation 1 is supposed to be labeled as a general sensitive bit and not a specific ASD region so I was expecting that result. I'll attach a smh file that has regions 2,3,4 declared. It works exactly how its supposed to. I am able to use it to do targeted fault injection and view the sensitivity map in the Quartus_fid gui. I can't attach a smh file of one with more regions declared since they never generate.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I not sure why. I am not able to duplicate the problem here. Can you share me your design file? QAR file. Perhaps you could private message me the design.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page