- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

I'm using the DIB to inter connect between the 2 dies of the Stratix 10

I'm using it in BYPASS (therefore I need to define the constraints) mode and one of the IO is transferring clock from one side to another - source synchronous.

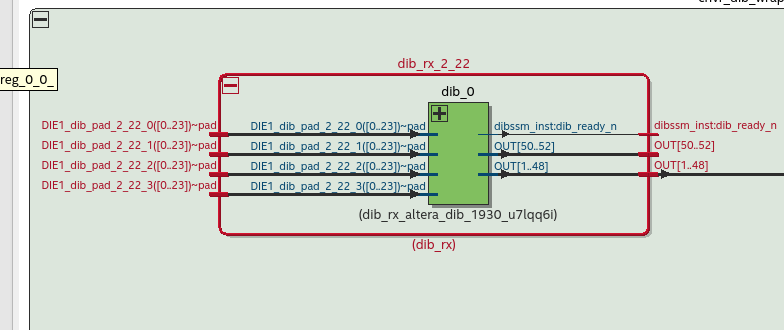

I generated DIB Module from the IP catalog (dib_rx_altera_dib_1930_u7lqq6i)

at the synthesis / fitter stage I would like to assign the constraints to the IO

the question is to where should I assign / define the Clock in the constraints , and the input delay ?

to DIE1_dib_pad_2_22_2[18] or to OUT[18] (in the case of the Clock) , and similar to the input delay ?

if I will assign Input Side DIE1_dib_pad_2_22_2[18] - will quartos/ timing analyzer will understand that OUT[18] is a clock (and take into account the routing delay) ?

or the dib_0 module is Blackbox for the timing analyzer and I should define the clock and IO input delays on the OUT[18] ?

my understanding that the input from the EMIB inserted to the Die1 via DIE1_dib_pad_2_22_2[18] , dib_0 module does nothing in bypass mode (just routing) , and the OUT[18] is the continuation of the wire .

thanks

Or.

- Tags:

- constraints

- DIB

- IO

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I cannot seem to get engineering to confirm the values, but the normal practice is by adjustment.

You can start with the values they put for the example design and fine tune it after compilation.

Below are the values used:

- max C=2.65

- min C=-2.65

- max A + max B = 8.25

- min A + min B = 3

- max D + max E = 4.75

- min D + min E = -1.64

Regards,

Nurina

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Please refer to this document for timing constraint guideline: https://www.intel.com/content/www/us/en/docs/programmable/683142/20-2-19-3-0/timing-transfer-for-bypass-mode.html

Regards,

Nurina

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm aware of this document ,

The document leaves many open questions , and does not refer to my questions.

- The document is talking about system synchronous and not Source synchronous as my case.

- I didn't find any place that specifies the values of B,C,D Timing values (at the Figure 16) the only timing which was specifies is 2.5ns, it is not written if 2.5ns = EMIB Delay (C values) , or the DIB Latency (B,D values) - or all the values together .

- My question was to where should I set the input/output delays practically in the SDC, which means to which pins or ports?, it is not written in the document , what is the dib_0 module (in my original question) stand for , is it the "Die B DIB" (at figure 16)? or it is " EMIB+DIE B DIB " ?

- The importance of item 3 above is to understand if quartos timing analyzer , takes into account the internal routing of dib_0 and derived the clock definition in the input side and add the Routing delay inside the dib_0 module

Thanks

Or

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Or,

Apologies for the late reply.

May I know which device you are targeting? Can you provide the OPN?

Thanks,

Nurina

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

1SG10MHN3F74C2LG_U1,

1SG10MHN3F74C2LG_U2,

Thanks

Or.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Or,

- The clock should be virtual clocks, so there shouldn't be a target. You just need to define the period and name of the clock and Timing Analyzer will create a virtual clock.

- What do you mean by system synchronous, how is it different from your source synchronous design?

- The B,C,D timing values from Figure 16 of the above document is as follows. B=D=DIB Latency=2.5ns as mentioned here https://www.intel.com/content/www/us/en/docs/programmable/683142/20-2-19-3-0/latency.html. EMIB Delay=C=Wire Delay of Stratix 10

- The set_input/output_delay should be targeting the virtual clocks and the ports connected to DIE1_dib_pad_2_22*

- <<my understanding that the input from the EMIB inserted to the Die1 via DIE1_dib_pad_2_22_2[18] , dib_0 module does nothing in bypass mode (just routing) , and the OUT[18] is the continuation of the wire .>> Is this specific to your design? If not, then you may apply the timing constraints as suggested above.

There is a DIB IP example design, you can generate this in the Platform Designer. You may refer to this example design for the timing constraints.

Regards,

Nurina

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Nurina

- Clock should be assign to IO – when constraining Source Synchronous interfaces

Look at this training and document and trainings from Intel/Altera.

Slide 12,27

https://cdrdv2-public.intel.com/653688/an433.pdf

Section Output Clock Constraints and Input Clock Constraints

- in System Synchronous – the clock is not transferred with the Data (as in Source Synchronous) – in system Synchronous the clock is transferred to both devices , and should be aligned.

- where can I find “EMIB Delay=C=Wire Delay of Stratix 10” Values , I search and find nothing about it . which document describes it ?

Searching for EMIB in this document finds nothing.

- This is not accurate according to “Source Synchronous interface “ - see course and document above .

The output delays of the “Transmitting Device “ is assign to the clock which defined on the output Pin . / Slide 26 ,31 at the training

For the Receiving Device ,you are right, the input delay is according the virtual clock .

- This is not specific from my implementation this is Module I get when I generated the DIB module .

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Or,

In Bypass mode, there is no clock transfer involved. In bypass mode, this IP essentially acts as a wire between 2 dies with one reference clock, so it isn't system synchronous. In figure 16 of the following document, you can see that there is an IOPLL in both dies, implying that this is also a source synchronous design https://www.intel.com/content/www/us/en/docs/programmable/683142/20-2-19-3-0/timing-transfer-for-bypass-mode.html

How are you using the DIB IP? Are you sure you should be using bypass mode, not synchronous mode?

In figure 16 of the above document, you can see that the EMIB delay is the propagation delay between two dies. It is mentioned in this document that it's the wire delay https://www.intel.com/content/www/us/en/docs/programmable/683142/20-2-19-3-0/bypass-mode.html

I don't have access to the slides, I'm not sure if you can share a snapshot here either.

Can you share your project so I can understand how you are using it?

Thanks,

Nurina

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Nurina.

1. the course / Slides are intel's course how come you dont have access to something that intel publish .

do you have access to this web page :

https://learning.intel.com/Developer/pages/30/all-intel-developer-training

then search :"constraining source synchronous (E-Learning) " and see the course

this course will explain you what is source synchronous and the constraints you need to assign (in general not on DIB specifically )

in addition you can read the document from Intel - attached it now since somehow you can not load it .

I recommend that you do the course first .

2. I'm using ByPass mode of DIB - which means using the DIB as "cable connection" or "replacing cable" , on the DIB you can transfer data , but you can also transfer clock along the data - not as points to the document which is synchronous design . (please watch the course or read what is source synchronous ) . when you transfer clock you have different constraints you need to assign for the input and output delay.

3. Regarding the delay. you are confusing me in your answer .

at your first answer Quotation "The B,C,D timing values from Figure 16 of the above document is as follows. B=D=DIB Latency=2.5ns as mentioned here https://www.intel.com/content/www/us/en/docs/programmable/683142/20-2-19-3-0/latency.html. EMIB Delay=C=Wire Delay of Stratix 10"

B, D are 2.5 ns DIB Latency what was missing is the EMIB Delay(C , Wire Delay) , and then in your last answer , you sent me to a document which is again talking about DIB Latency and NOT EMIB Delay ...

Quotation from the Document .... "The latency between DIB pins is 2.5 ns."

so Intel Document is missing the finial numbers of DIB Latency and EMIB Delay ... what is the total delay B+C+D = 7.5ns / B+C =5ns or just C=5ns ...

even if working with system Synconus as in the example here: https://www.intel.com/content/www/us/en/docs/programmable/683142/20-2-19-3-0/timing-transfer-for-bypass-mode.html

you need the Value B , C , D which are not described in the document ... (there only vouge number 2.5ns from the document quotation "The latency between DIB pins is 2.5 ns." which is not understood to what parameter it is set .

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Or,

Apologies on the confusion. I am discussing on the appropriate usage with the internal team for some clarity.

Can you please share your design for both dies? If it's confidential, you can share it through email. I'm sending you an email, please check.

I would like to understand how the DIB IP is used in your case.

Thanks and regards,

Nurina

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

- any update about my technical questions ?

- did you get my qar file of my design ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Or,

Yes, I'm able to receive your design, I'm still waiting for internal team's response. I will let you know of any updates.

Regards,

Nurina

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Or,

I'm currently waiting for internal team's response, I'll let you know of any updates.

Regards,

Nurina

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Or,

Apologies for the late response. Engineering team doesn't recommend transferring the clock signal as the uncertainty on the clock path will be too high to reasonably close timing. It is better to just send a delay matched clock to each die.

Can you confirm- are you trying to have one clock source in one die and have the signal transferred to the other die?

If you were to refer to the example design generated in IP catalog/Platform Designer, you'll be able to see the constraint values used for DIB IP. However these constraints are for 50MHz operation. From your project I can't tell what speed you intend the DIB IP to run on.

Regards,

Nurina

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Nurina,

1. the clock is 13.3Mhz .

2. what is "delay matched clock to each die." ? - send same clock to both dies , but what is the meaning of delay ?

3. Yes I'm trying to have one Clock Source in Die 0 , and transfer the data along with the clock via the DIB to the other Die.

4. even we move to "System Synchronous" (I guess this is what you suggest in "Delay Matched Clock" I'm still looking for the values - see item 3 at my post at "01-03-2023 03:54 AM"

BTW it is not written in any document that DIB does not support Clock Transfer via DIB - and now we need to do Huge change in my design - I recommend that Intel will comment about that .

in addition , can you tell if I need to define special parameters when I generate example design ? where can I find the constraints of the 50Mhz you wrote above ?

Or.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Or,

What I mean by delay matched clock is that the clock hitting the clock pin of each die is matched. Best way to do that is to have a clock gen on your board with two matched outputs and route those signals to each die with matched trace lengths. That ensures that each FPGA has a clock coming in that's matched.

In this case you wouldn't need the DIB IP at all.

It is possible to send a clock over from one die to another using DIB IP, but due to high clock uncertainty, it will be very difficult to ensure the proper timing constraints and addressing any potential CDC. There is a high chance of hardware failure which is why I'm suggesting against sending a clock over through DIB IP.

To generate the example design, go to Project>Upgrade IP Components and double click on the DIB IP and Quartus will open IP Parameter Editor. At the toolbar go to Generate>Generate Example Design. Once generating the example design, you can run a compilation and take a look at the SDC file in the example design. The example design will use 50MHz clock by default.

Regards,

Nurina

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

regarding your comment : "In this case you wouldn't need the DIB IP at all."

- if I get you right , you mean that I don't need DIB IP for sending clock from die to die ?

, but I do need DIB IP for transferring data from Die to Die (I dont see other way to transfer data )

Or.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Or,

Yes that is right.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

do you have answer for the timing values of B,D,C values at figure

my request from 01-03-2023 ...

thanks

Or.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I cannot seem to get engineering to confirm the values, but the normal practice is by adjustment.

You can start with the values they put for the example design and fine tune it after compilation.

Below are the values used:

- max C=2.65

- min C=-2.65

- max A + max B = 8.25

- min A + min B = 3

- max D + max E = 4.75

- min D + min E = -1.64

Regards,

Nurina

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I’m glad that your question has been addressed, I now transition this thread to community support. If you have a new question, Please login to https://supporttickets.intel.com , view details of the desire request, and post a feed/response within the next 15 days to allow me to continue to support you. After 15 days, this thread will be transitioned to community support. The community users will be able to help you on your follow-up questions.

p/s: If any answer from community or Intel support are helpful, please feel free to mark as solution, give Kudos and rate 4/5 survey

Regards,

Nurina

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page