- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I'm planning to use several triple speed ethernet Mac IPs but as far as i could see, you can't use Tile transceivers to do that. So i tried to compile my design with TSE (lvds io with integrated serdes).

I managed to implement 8 tse at once but i could not with 16 of these as the fitter was unable to find enough IO to do that. I suspected that the number of IOPLL was unsufficient but i read there was 32 differentials of them.

I don't know how to fix this problem.

Also, i ask if there is way to use H-Tile transceivers to implement SGMII protocol. I know it sounds weird to implement such a low speed interface but i need the large computing capabilities of the S10MX.

Thank you,

regards,

john

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thank you for your reply.

i am using the 1SM21BHU2F53ES2 for test purposes (Stratix 10 MX FPGA Development Kit). I didn't assign any IOs at first as the planner can do it automatically.

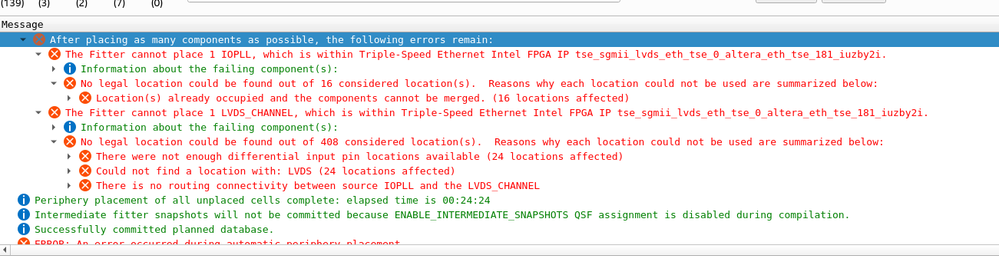

see the error i get during plan stage :

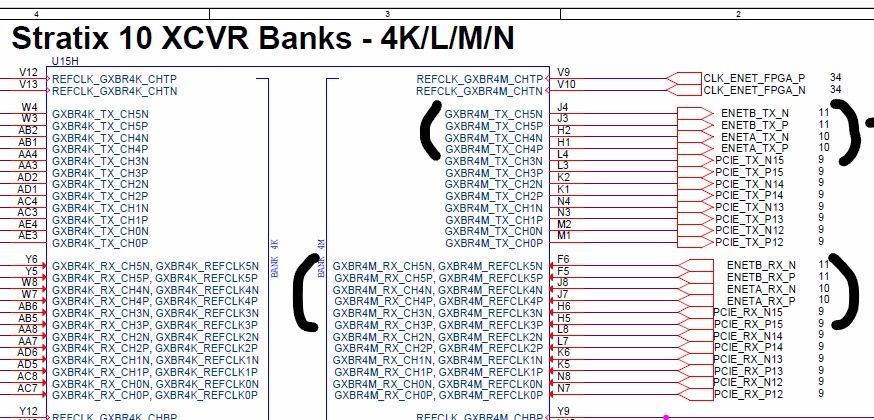

I was asking about the Tile transceivers because i downloaded an example design from INTEL (Stratix 10 SoC fpga devkit, schematic p.13) where IOs for the triple speed Ethernet were connected to dedicated transceivers(GXBR4M_RX_CH4P, GXBR4M_REFCLK4P for example).

Thank your very much dlim

Best regards,

john

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi John,

1) For the fitter error

- As I suggested earlier, you can try check the resources from the passing 8 TSE design first

- Or if you need my help to debug further on 16 TSE design fitter error, then kindly pls send me your 16 TSE design QAR file so that I can review your design further to understand the root cause

2) For TSE IP connecting to XCVR channel

- As you can see from the attached TSE IP screenshot, only LVDS IO option is supported, not transceiver channel

- I am also curious why the S10 SOC example design mentioned TSE IP can be connected to transceiver channel. Can you share with me the link of the TSE example design then I can take a look into it ?

Thanks.

Regards,

dlim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi dlim,

1) I found a limit of 14 TSE IPs. After this number, the fitter could not find a suitable scheme for pin assignements. (it seems you can drive only 1 PLL per bank, i think i read this limitation somewhere in a datasheet )

I sent you the .qar file of my early design with 15 TSE LVDS IO.

2) There is no design example provided with S10 soc kit which instanciates a TSE IP with LVDS IO. However, you can see in golden_top design (see the attached qar) that sgmii pins are linked to gxb transceivers. Those ones may be used with a 1G/10G phy design but there is no example which explicitly shows how it has been implemented.

Maybe, you can tell me more about this.

Thank you,

Have a nice day,

regards,

John

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi John,

Thanks for sharing the design file. Pls see my reply below.

- For the fitter error

- I can't compile your design due to missing "nios_with_4_tse_sgmii_lvds_avalon_interface_camera_0.ip" file

- Anyway, you are right on one IOPLL is available per one IO_BANK. You can refer to below user guide doc "figure 2"

- https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/stratix-10/ug-s10-gpio.pdf

- For your selected S10 MX FPGA. the max available IOPLL is 15 as shown in attached pinout file pic. That means you can generate max of 15 TSE IP where one TSE IP will consume one IOPLL

- For connecting 1G Ethernet to transceiver (XCVR) channel. Let me clarify again on below 2 options

- If you are using TSE IP - then user can only connect to LVDS IO, not XCVR channel

- If you are using 1G/2.5G/5G/10G Multi-rate Ethernet PHY Intel FPGA IP - user can connect to XCVR channel

- Example design of Multirate PHY IP is available in below link. The example design comes with both PHY and MAC together

- https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug-20073.pdf

Thanks.

Regards,

dlim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi dlim,

sorry for the missing .qsys in the qar file. Anyway, now i know how many TSE i can implement with lvds io. Thank you for that.

For the multi-rate design, i was checking this option as an alternative. The X557 AT4 phy seemed to fit my needs, but i am quite lost in the datasheet (KR, sgmii, connect to lane 0 for sgmii, ok but what if i want to use 10G, and so on) . I did some research on google and multiple vendors used it for their networking products.

So, my last inquiry would be : where can i find some help to interconnect the multi rate phy on s10 and the x557 phy as quickly as possible? 😅

For now, i have multiple distant FPGAs with 88E1111 phy which can run at "only" 1Gbps.

Thank you very much dlim,

Have a nice day.

Best regards,

John

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi John,

Thanks for showing interest with Intel product.

- For configuring 10G MAC and Multirate PHY

- You can refer to the example design link that I shared with you

- For configuring Intel X557 AT4 PHY chip

- I know you maybe thinking we all are intel support agent but in reality Intel is a very big company with different organization in charge with different product.

- Feel free to consult me on FPGA IP related question but I am not familiar with Intel X557 AT4 PHY chip.

- However, I do find out about another Intel forum supporting Intel Ethernet product. You can post your question there and ask for help. Other Intel agent from the Ethernet product line should jump in and help you up

- https://forums.intel.com/s/topic/0TO0P00000018NbWAI/intel-ethernet?language=en_US

Thanks.

Regards,

dlim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Many thanks dlim,

have a nice week.

Best regards,

John

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page