- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

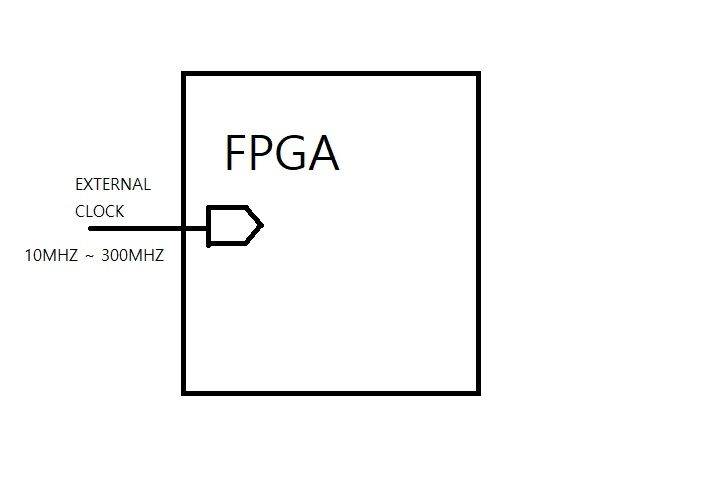

My design need a external switching clock, which is an input clock that can externally reset its clock rate.

I need to constrain this clock, but I don't know how to do it..

ryan scovil' timequest userguide or source synchronous guide doesn't show me the way to constraining this..

I think there's one way to do that, which is to use pll reconfig. The input clock will be the external clock and the c0 clock will use the same clock as the input clock. but is this the only way?

Let me know if there's any other way. THANK YOU

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Are you saying that the input clock can be anything between 10 MHz and 300 MHz? If so, you'd probably want to constrain for the fastest clock (replace ext_clk with the name of your top-level clock port:

create_clock -name ext_clk -period 3.3 [get_ports ext_clk]

Then, if it's going through a PLL, just use:

derive_pll_clocks

#iwork4intel

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Are you saying that the input clock can be anything between 10 MHz and 300 MHz? If so, you'd probably want to constrain for the fastest clock (replace ext_clk with the name of your top-level clock port:

create_clock -name ext_clk -period 3.3 [get_ports ext_clk]

Then, if it's going through a PLL, just use:

derive_pll_clocks

#iwork4intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page