- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi ,

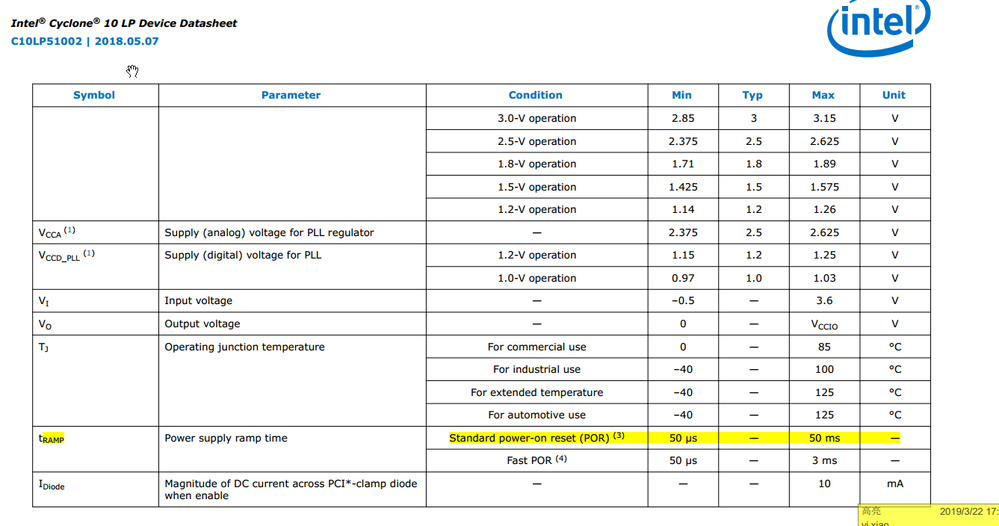

We use 10CL055YU484C8G. MSEL sets as Standard POR mode, datahseet reqiures ramping time of power supply to be within 50us~50ms.

Is this requirement apply for each single power rail's t_ramp or Total t_ramp time of all rail?

Thanks!

1 Solution

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Do you mean that the sum of all power rails' t_ramp should be within 50us-50ms?

Yes

Link Copied

6 Replies

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

UP

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

another question is , if the power rail ramps up too fast (<50us) or too slow(>50ms), what may happen? Thanks.

We now have a LDO desgined for VCCA_PLL_2V5 for 10CL055YU484C8G , whose ramp time is rather short, about 30us or so. That's is my worry.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

up

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Total supply attached to the POR monitoring supply

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi RSree,

Do you mean that the sum of all power rails' t_ramp should be within 50us-50ms? Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Do you mean that the sum of all power rails' t_ramp should be within 50us-50ms?

Yes

Reply

Topic Options

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page