- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi.

In my project I use Arria 10 FPGA.

I receive 9953.28Mbit/s stream on Transceiver and I need to retranslate it with the same speed(no idle). RX clock is not ideal, what is why I can`t use internal reference clock for TX.

As I understand, I need to use RX recovered clock as a clock for TX, but not sure how I can do that.

Is this OK, If I use parallel rx_clkout_clk as input for FPLL and connect to tx_serial_clk0_clk?

Or I need use high speed serial RX recovery clock from CDR as TX clock?

Best regards.

Link Copied

3 Replies

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

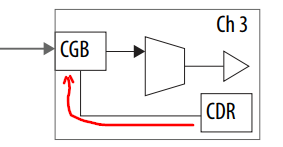

As I understand in ug_arria10_xcvr_phy(page 385), the local CGB is feeded by CDR, but I cant find clk output from CDR

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thank you for contacting us. Allow me some time to look into your issue. I shall come back to you with findings.

Thank you for your patience.

Best regards,

Chee Pin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

As I understand it, you seems to have some inquiries related to re-transmit of data using the same clock domain as the received data. For your information, the GXB refclk would need clean clock. Based on my understanding, you would need to feed the RX recovered clock to an external clock cleaner on board, then feed the cleaned clock back to the TX refclk.

Please let me know if there is any concern. Thank you.

Reply

Topic Options

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page