- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi all,

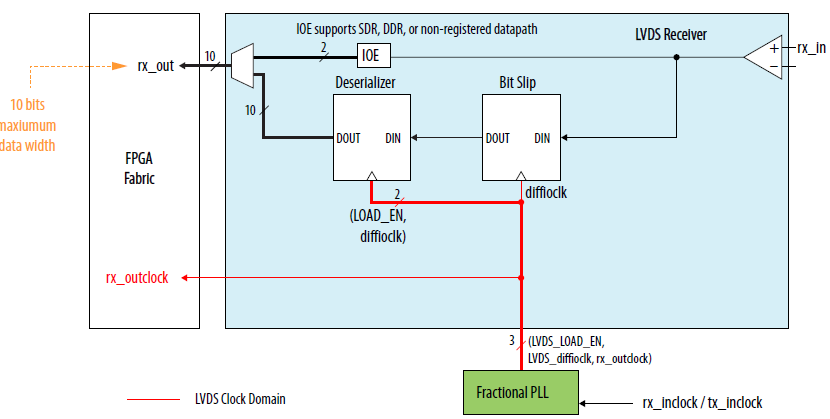

In a recent project I would like to use a camera with a clock of 290 MHz when using Double Data Rate. The throughput rate is therefore 580 Mbps per channel for a total of 10 channels. Now it would be helpful if I could use the transceivers in the Cyclone V for deserialization.

Currently, I use the DDIO IPs, sometimes giving me timing problems. While the design may fits when using multiple seeds, I think using the transceivers might be helpful to avoid problems.

The datasheet of the transceivers specifies a minimum data rate of 612 Mbps for the receiver. How does the data rate come about and could I eventually use the transceivers?

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

thanks for your answer.

The document "Cyclone V Device Interfaces and Integration Document" describes that "the In SDR and DDR modes, the data width from the IOE is 1 and 2 bits, respectively". As a result, the LVDS Reciever does not use the data path with the deserializer for my DDR data input. In my understanding, the design would then be routed just like mine, which uses the DDIO blocks.

I have to say that I drive the DDIO IP directly with the clock from the input pin and no intermediate PLL for the data clock. Can this possibly fix the timing issues? I initially tried to use the PLL, but I was overwhelmed by setting the constraints associated with the DDIO block.

Best regards,

Christian

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Chee,

Finally, I changed the FPGA desgin a bit to get it more stable. Since the data source in this case is a camera, I will successively increase the frame rates and resolutions and check up to which configuration the FPGA design works. I will not use the PLL for now, but keep it in mind. The information that the deserializers do not work for this case answers my primary question. Thanks for the support.

Best regards,

Christian

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page