- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi everyone,

to realize an asynchronous project,

I would need to manage different signals and understand when they change state, both from 0 to 1 and from 1 to 0.

The change from these signals should change an output signal,

which drives another section of the circuit.

For this, I use:

process(signal_1)

begin

if something then

signal_out <= '0';

end if;

end;

process(signal_2)

begin

if something then

signal_out <= '1';

end if;

end;In this case, I obtain an error:

Error (10028): Can't resolve multiple constant drivers for net "signal_out" .

For this reasons I try to insert all signals in one process, in this manner:

process(signal_1, signal_2)

begin

if rising_edge(signal_1) or falling_edge(signal_1) then

if something then

signal_out <= '0';

end if;

end if;

if rising_edge(signal_2) or falling_edge(signal_2) then

if something then

signal_out <= '1';

end if;

end if;

end;

But, in this case, I have the error:

Error (10628): […] can't implement register for two clock edges combined with a binary operator.

What is the correct way to get what I want?

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Well, these are typically beginner mistakes in VHDL coding.

- A signal/variable cannot be updated in two different Processes.

- A signal/register/variable cannot be assigned values at both clock edges of two different clock signals.

process (signal_1, signal_2) begin

if(signal_1) then

signal_out <= 0;

else

signal_out <= 1;

end if

end process;In the above code, there's an issue... signal_out gets assigned 0 when signal_1 =1 and irrespective of signal_2. Same goes for the else condition. To avoid, this we have to specify all logically exclusive conditions in the if-else loop.

process (signal_1, signal_2) begin

if(signal_1 == '1' and signal_2 = '0') then

signal_out <= 0;

else if (signal_1 == '0' and signal_2 == '1') then --left out conditions are sig_1 = sig_2 == 1 , sig_1 = sig_2 == 0.

signal_out <= 1;

end if

end process;

Normally, you assign signals on the rising edge or falling edge of a periodic signal like a clock and have the other signal in the sensitivity list of the process as the reset so that the Flops in the design can be reset to a known state on Power ON.

process( clock, reset) begin

if(reset == '0') then

signal_out <= '0';

else if (rising_edge/falling_edge clock) then

signal_out <= '1'

end if

end processThis will make sure that the code infers flip-flops and not larches or other combinational logic that is unwanted (unless or course you are designing combinational circuits, in which case you would code it in a different way.)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for your answer.

What I try to do is change signal_out when signal_1 or signal_2 change their state.

It is assumed that signal_1 and signal_2 CANNOT change at the same time.

In the first case, if signal_1 changes, then signal_out must be set to 0. In any case, both that signal_1 goes from 0 to 1, and that it passes from 1 to 0.

It's an asynchronous design and I'm not using any clock.

Can I do this with the code you showed me?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Can I use this code? It is correct?

process (signal_1, signal_2)

begin

if signal_1 = '0' or signal_1 = '1' then

signal_out <= '0'

end if;

if signal_2 = '0' or signal_2 = '1' then

signal_out <= '1'

end if;

end;

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

if possible please provide the project file, that will help us to better support.

if you don`t want to share it in community, you can use "My Messages" option to share with me.

Regards,

Vikas

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The basic problem is that I would like to implement the 2-phase handshake protocol.

For this reason, I need to understand when a signal changes state.

Is it possible to capture an event that indicates that the signal has changed its logic level?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

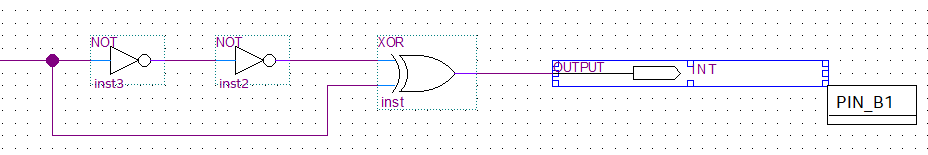

It is possible to make a edge detector in VHDL? I think that It can to resolve the problem.

The Edge detector is a circuit like this:

Can I make it in VHDL?

I try with:

process (myInput)

begin

If (not (not myInput)) xor myInput = '1' then

--Edge detect!

end if;

end process;

but this code do not compile/work (Error (10476): VHDL error at Control.vhd(90): type of identifier "MyInput" does not agree with its usage as "boolean" type)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Could you check with .vhd file generated from .bdf file?

Open .bdf file( as designed in previous post) in Quartus & then,

"File" Menu->"Create/Update"->"Create HDL design file from current file(VHDL",

Regards,

Vikas

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page