- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I am using Quartus Prime v19.1 Standard Edition.

I can see in Quartus Timing Analyzer that I have an unconstrained clock, more specifically the following one:

adbg_top:dbg_top|adbg_wb_module:i_dbg_wb|adbg_wb_biu:wb_biu_i|str_sync_wbff2

I wanted to add a command in my SDC to false_path it, so I tried the following:

set_false_path -from [get_pins {dbg_top|i_dbg_wb|wb_biu_i|str_sync_wbff2}] -to [get_pins *]

The command does not work as Timing Analyzer complains about "Argument <from> is an empty collection".

Moreover, when I am trying to run the following command in Timing Analyzer:

get_pins {dbg_top|i_dbg_wb|wb_biu_i|str_sync_wbff2}

I get back a message saying it could not be matched with a pin. How is that possible? Is it because of optimization of Quartus during the Compilation of the design? Then why does it output the initial name and not the final after the optimization? How can I false_path it in first place?

It is not clear at least to me, how the "get_pins" command works.

Can anyone explain? I should mention that Quartus is really challenging when it comes to TCL commands.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

After several tries I managed to "find" the Q pin of the register by using the "-compatibility_mode" option of the "get_pins" command. This is the one that helps traverse the hierarchies of modules, and the command I used was the following:

get_pins -compatibility_mode dbg_top|i_dbg_wb|wb_biu_i|str_sync_wbff2|q

where "str_sync_wbff2" is the name of the register and "q" is the output of the ff that acts as a clock.

After that I was able to apply a constraint on it.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Update,

I tried the following:

reg str_sync_wbff2 /* synthesis noprune */;

and

reg str_sync_wbff2 /* synthesis preserve */;

In order to prevent Quartus from optimizing this register. Both of them did not have any effect as I am not able to trace the pin with get_pins. Is this the expected behavior from Quartus?

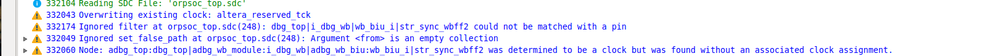

Moreover, I get the following messages:

How is that even possible? At first not being able to find the pin and immediately after determining that this pin is a clock?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

After several tries I managed to "find" the Q pin of the register by using the "-compatibility_mode" option of the "get_pins" command. This is the one that helps traverse the hierarchies of modules, and the command I used was the following:

get_pins -compatibility_mode dbg_top|i_dbg_wb|wb_biu_i|str_sync_wbff2|q

where "str_sync_wbff2" is the name of the register and "q" is the output of the ff that acts as a clock.

After that I was able to apply a constraint on it.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You can also use -hier which is used to search all hierarchical levels of the timing netlist using wildcards. In general, though, using the GUI to find and target stuff like this will make your life much easier. If you're not familiar with it, in the Quartus Text editor, in a .sdc file, go to Edit->Insert Constraints and choose one. The browse buttons in those dialogs open the Name Finder which lets you easily search the netlist, including enabling the compatibility mode or hierarchical search options.

As far as your design is concerned, though, why do you want to false path something the tool is indicating as a clock (unless I'm reading your last post incorrectly and that once you were able to find the pin you put a clock constraint on it)?

#iwork4intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @sstrell

thank you very much for your reply, it is much appreciated.

No your intuition is right, I am applying a "false_path" on it.

This is the Bus Interface Unit of the "Advanced Debug Interface" (Opencores). As it is not my design, my initial thought was to keep it as is.

As you can see in the attached file, there is a register "str_sync_wbff2" which Quartus complains about being a clock. This register is assigned to a wire "start_toggle" and this wire exists in the sensitivity list of an "always" block.

So this is why the tool interprets it as a clock. Nevertheless, I think the intention of the designer was not for it to be accounted as a clock.

As you can imagine there are clocked paths associated with this register since the "adbg_wb_biu" module operates with two "official" clocks:

tck_i --> is the clock coming from the JTAG cable

and

wb_clk_i ---> is the clock of the Wishbone bus, generated by an Altera PLL.

So my first idea was to false path all the paths from this generated clock (str_sync_wbff2), to all the paths of the other 2 clocks and see if get the intended behavior.

I think that for FPGA designs it is a general advice to not over-constrain the design, so making it a "false_path" was the simplest I could do.

This Debugger is part of a larger implementation, an OpenRISC processor, that I am trying to implement. So there are different designs combined together. This is my very first attempt.

Always feel free to add your thoughts, I am happy to discuss.

Kind regards,

anm

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page