- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi I have gone through the UG :Intel® Arria® 10 DisplayPort IP Core Design Example User Guide

UG-20075,

In this it uses fpll and stores calibrated link rates for different speeds,

can we implement same to the ATX PLL, storing link rates , if yes

Please share the example design or document.

Regards,

Rajesh

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Rajesh,

As I understand it, you have some inquiries related to storing link rates in ATX PLL. Please correct me if I am wrong, I believe you are referring to dynamic reconfiguring the ATX PLL to different data rates. If yes, for your information, ATX PLL supports multi-profiles reconfiguration. In other words, you can preconfigure a number of frequency profiles and by writing to a few registers, it will auto reconfigure for you. You may refer to section "Multiple Reconfiguration Profiles" and "6.5 Embedded Reconfiguration Streamer" in the A10 Transceiver PHY User Guide for further details.

Please let me know if there is any concern. Thank you.

Best regards,

Chee Pin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

In Multiple Reconfiguration Profiles i have to calibrate after changing from one profile to other.

from the example code given by Displayport, It will save link rate dynamically switches between different speeds without calibration.

can we do that same with multiple profiles ? can we save calibration results ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Rajesh,

Thanks for your update. You are right. After performing the dynamic reconfiguration for ATX PLL, you should perform a recalibration to ensure it can function properly. As for the saving of calibration results, sorry as I am not aware of this with the ATX PLL. Probably the example code on Displayport has some customization prepared by Factory.

Please let me know if there is any concern. Thank you.

Best regards,

Chee Pin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

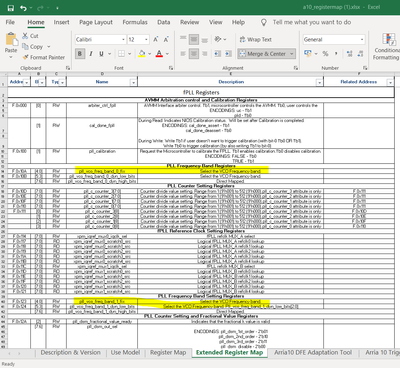

In display port design for FPLL is used, which having registers to store the frequency band, the similar registers are not available for ATX PLL.

SNAPSHOT FROM A10 register map excel sheet.

I need to figure out whether i can use the existing logic from display port for switching speed when i use ATX PLL?

or i must use only "Multiple Reconfiguration Profiles" for switch between the speed ?

If possible, please confirm from internal team about my query!

Regards,

Rajesh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Rajesh,

Regarding your latest inquiry if you can use the existing logic from display port for ATX PLL, sorry as I do not have visibility into the display port logic and could not really comment. However, based on my understanding, ATX PLL and fPLL should have differences in the internal architecture and registers, I believe you cannot directly use the existing logic.

I would suggest you to open a new thread with request specific to replacing ATX PLL in the DP IP generated design example so that our DP expert could further assist.

Please let me know if there is any concern. Thank you.

Best regards,

Chee Pin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

<I believe you cannot directly use the existing logic>

Yes i cannot, i will modify the logic

but Does ATX pll supports storing link rate feature ?

Regards,

Rajesh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Rajesh,

Regarding the ATX PLL storing link rate, Multiple Reconfiguration Profiles is one of the feature supported. Another workaround would be for user to identify the list of registers that need to be changed from a rate to another rate. Then create own controller and perform direct read-modify-write to the target registers. With this method, you can reduce the processing time because you are only changing affected registers. However, the drawback is that you need to code your own controller and need to change the right registers to avoid ATX PLL malfunction.

Please let me know if there is any concern. Thank you.

Best regards,

Chee Pin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for quick response,

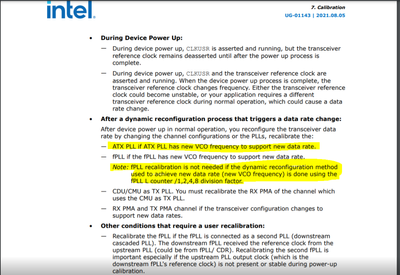

From A10 transceiver user guide,

For FPLL only having the feature of storing cerebrated results, For ATX PLL calibration is needed to support new VCO frequency.

so if i change the VCO frequency by changing M,L,N counter values(perform direct read-modify-write to the target registers) for ATX PLL i need to recalibrate after changing from one to other frequency!

Regards,

Rajesh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Yes, your understanding is correct. ATX PLL need to be recalibrated after a rate change.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page