- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I am going to get a new workstation (probably sandy bridge) which can enable me to measure

CPU and DRAM power. Can anybody tell me the combination of processor+motherboard which will have these

abilities.

An option that I have looked up is

1.http://www.newegg.com/Product/Product.aspx?Item=N82E16819115234 with http://www.newegg.com/Product/Product.aspx?Item=N82E16813121606

Please help me with a good configuration.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Every sandybridge or later (ivybridge) will let you estimate the power of total processor package, the cores and usually graphics unit.

The DRAM measurement is a server only feature and you have to have the correct bios to enable the feature.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Patrick Fay (Intel) wrote:

Every sandybridge or later (ivybridge) will let you estimate the power of total processor package, the cores and usually graphics unit.

The DRAM measurement is a server only feature and you have to have the correct bios to enable the feature.

Thanks much for your reply. Is their any particular motherboard that supports DRAM power measurements?

Let me know if there is one.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

It is BIOS dependent not motherboard.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

See please The Intel® Server Board S2600CP BIOS manual (page 99). The option enables DRAM RAPL energy counters.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for the reply Roman. Will the Intel Xeon E5-2600 processor series work with this motherboard?

Thank You.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Also, I saw some documents related to Intel node power manager

Will getting a server motherboard which supports this enable getting DRAM power consumption on the fly?

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Also, I saw some documents related to Intel node power manager

Will getting a server motherboard which supports this enable getting DRAM power consumption on the fly?

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

gokussj9 wrote:

Thanks for the reply Roman. Will the Intel Xeon E5-2600 processor series work with this motherboard?

Thank You.

Yes of course.

Web link:http://www.intel.com/content/www/us/en/motherboards/server-motherboards/server-board-s2600cp.html

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, I am working with HP Proliant DL380p Gen8 series with processor Intel(R) Xeon(R) CPU E5-2670 0 @ 2.60GHz . Are the DRAM RAPL readings exposed when using other motherboards/platforms which are not intel based ?

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I t could be Bios vendor dependent.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Patrick Fay (Intel) wrote:

Every sandybridge or later (ivybridge) will let you estimate the power of total processor package, the cores and usually graphics unit.

The DRAM measurement is a server only feature and you have to have the correct bios to enable the feature.

Hello,

I am currently using centos 6.6 (desktop) on my PC. I have Intel i7 processor. I checked my BIOS with "dmidecode" and it gives me

# dmidecode 2.12

SMBIOS 2.6 present

My aim is to measure DRAM power for particular application i.e. Power on the fly.

Is it possible to measure DRAM power on this machine?Or Is it required to install CentOs server? Kindly correct me if I am wrong.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

What is your CPU's cpuid brand string? The string like on my laptop 'Intel(R) Core(TM) i5-3427U CPU @ 1.80GHz'.

This will tell us the architecture and target system type (client, server, etc) for the chip.

Pat

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

And just to provide some info.

I also have a Haswell based ultrabook with a 'Intel(R) Core(TM) i5-4350U CPU @ 1.40GHz'. This is the 4th Generation Intel(r) Core(tm) Processor based on Mobile U-Processor and Y-Processor Lines. This system has the some DRAM energy info registers in the datasheet vol 2. Google 4th-gen-core-family-mobile-u-y-processor-lines-vol-2-datasheet.pdf

I don't know how much being able to use the registers depends on the BIOS. The haswell-based ultrabook I have is an internal system (not a system available for sale).

From the datasheet table of contents:

4.2 MCHBAR Registers Summary................................................................................ 245 4.2.1 DDR—DDR timing................................................................................... 247 4.2.2 DDR—DDR Rank Timing........................................................................... 247 4.2.3 PM—Power-down configuration register...................................................... 247 4.2.4 TC—Refresh parameters...........................................................................248 4.2.5 TC—Refresh timing parameters................................................................. 248 4.2.6 PM—Power Management DIMM Idle Energy.................................................248 4.2.7 PM—Power Management DIMM Power Down Energy.....................................249 4.2.8 PM—Power Management DIMM Activate Energy...........................................249 4.2.9 PM—Power Management DIMM RdCas Energy............................................. 249 4.2.10 PM—Power Management DIMM WrCas Energy........................................... 250 4.2.11 MAD—Address decoder Channel configuration register................................250 4.2.12 MAD—Address decode channel 0............................................................. 250 4.2.13 MAD—Address decode channel 1............................................................. 251 4.2.14 PM—Self refresh config. register.............................................................. 252 4.2.15 DDR—DDR_PTM_CTL_0..........................................................................252 4.2.16 DRAM—DRAM_ENERGY_SCALEFACTOR_MCHBAR.......................................254 4.2.17 DRAM—DRAM_RAPL_CHANNEL_POWER_FLOOR_MCHBAR...........................254 4.2.18 DDR—DDR_THERM_PERDIMM_STATUS.................................................... 254 4.2.19 DDR—DDR_WARM_THRESHOLD_CH0...................................................... 255 4.2.20 DDR—DDR_WARM_THRESHOLD_CH1...................................................... 255 4.2.21 DDR—DDR_HOT_THRESHOLD_CH0......................................................... 255 4.2.22 DDR—DDR_HOT_THRESHOLD_CH1......................................................... 256 4.2.23 DDR_THERM—DDR_THERM_INTERRUPT_STATUS...................................... 256 4.2.24 PACKAGE—PACKAGE_THERM_MARGIN.....................................................257 4.2.25 DDR—DDR_DIMM_TEMPERATURE_CH0.................................................... 258 4.2.26 DDR—DDR_DIMM_TEMPERATURE_CH1.................................................... 258 4.2.27 DDR - DDR-DIMM-HOTTEST-ABSOLUTE —DDR DIMM Hottest Absolute......... 258 4.2.28 DDR-DIMM_HOTTEST_RELATIVE—DDR DIMM Hottest Relative.................... 258 4.2.29 DDR—DDR_THROTTLE_DURATION_CH0................................................... 259 4.2.30 DDR—DDR_THROTTLE_DURATION_CH1................................................... 259 4.2.31 DDR—DDR_WARM_BUDGET_CH0............................................................ 260 4.2.32 DDR—DDR_WARM_BUDGET_CH1............................................................ 260 4.2.33 DDR—DDR_HOT_BUDGET_CH0............................................................... 260 4.2.34 DDR—DDR_HOT_BUDGET_CH1............................................................... 260 4.2.35 DRAM—DRAM_POWER_LIMIT..................................................................261 4.2.36 DRAM—DRAM_ENERGY_STATUS............................................................. 261 4.2.37 DRAM—DRAM_RAPL_PERF_STATUS......................................................... 262 4.2.38 PACKAGE—PACKAGE_RAPL_PERF_STATUS............................................... 262 4.2.39 PRIMARY—PRIMARY_PLANE_TURBO_POWER_POLICY................................. 262 4.2.40 SECONDARY—SECONDARY_PLANE_TURBO_POWER_POLICY....................... 263 4.2.41 PRIMARY—PRIMARY_PLANE_ENERGY_STATUS.......................................... 263 4.2.42 SECONDARY—SECONDARY_PLANE_ENERGY_STATUS.................................263 4.2.43 PACKAGE—PACKAGE_POWER_SKU.......................................................... 263 4.2.44 MSR—MSR_RAPL_POWER_UNIT.............................................................. 264 4.2.45 PACKAGE—PACKAGE_ENERGY_STATUS....................................................264 4.2.46 GT—GT_PERF_STATUS...........................................................................265

I've programmed a lot of the datasheet registers into my id_cpu utility. (The utility is not public.) Below is the output of the some of the DRAM related MCHBAR-based registers. I don't know if I've interpreted all the fields correctly but I gave it a shot.

Pat

chipset: MCHBAR: PM-Power Management DIMM Idle Energy: This register defines the energy of an idle DIMM with CKE on. Each 6-bit field corresponds to an integer multiple of the base DRAM command energy for that DIMM. There are 2 6-bit fields, one per DIMM. chipset: 0h MCHBAR: PM-Power Management DIMM Idle Energy: DIMM1_IDLE_ENERGY: This register defines the energy consumed by DIMM1 for one clock cycle when the DIMM is idle with cke on chipset: 3h MCHBAR: PM-Power Management DIMM Idle Energy: DIMM0_IDLE_ENERGY: This register defines the energy consumed by DIMM1 for one clock cycle when the DIMM is idle with cke on chipset: MCHBAR: PM—Power Management DIMM Power Down Energy: This register defines the energy of an idle DIMM with CKE off. Each 6-bit field corresponds to an integer multiple of the base DRAM command energy for that DIMM. There are 2 6-bit fields, one per DIMM. chipset: 0h MCHBAR: PM—Power Management DIMM Power Down Energy: DIMM1_PD_ENERGY: This register defines the energy consumed by DIMM1 for one clock cycle when the DIMM is idle with cke off chipset: 2h MCHBAR: PM—Power Management DIMM Power Down Energy: DIMM0_PD_ENERGY: This register defines the energy consumed by DIMM0 for one clock cycle when the DIMM is idle with cke off chipset: MCHBAR: PM—Power Management DIMM Activate Energy: This register defines the combined energy contribution of activate and precharge commands. Each 8-bit field corresponds to an integer multiple of the base DRAM command energy for that DIMM. There are 2 8-bit fields, one per DIMM. chipset: 0h MCHBAR: PM—Power Management DIMM Activate Energy: DIMM1_ACT_ENERGY: This register defines the combined energy contribution of activate and precharge commands. chipset: e9h MCHBAR: PM—Power Management DIMM Activate Energy: DIMM0_ACT_ENERGY: This register defines the combined energy contribution of activate and precharge commands. chipset: MCHBAR: PM—Power Management DIMM RdCas Energy: This register defines the energy contribution of a read CAS command. Each 8-bit field corresponds to an integer multiple of the base DRAM command energy for that DIMM. There are 2 8-bit fields, one per DIMM. chipset: 0h MCHBAR: PM—Power Management DIMM RdCas Energy: DIMM1_RD_ENERGY: This register defines the energy contribution of a read CAS command. chipset: a3h MCHBAR: PM—Power Management DIMM RdCas Energy: DIMM0_RD_ENERGY: This register defines the energy contribution of a read CAS command. chipset: MCHBAR: PM—Power Management DIMM WrCas Energy: This register defines the energy contribution of a write CAS command. Each 8-bit field corresponds to an integer multiple of the base DRAM command energy for that DIMM. There are 2 8-bit fields, one per DIMM. chipset: 0h MCHBAR: PM—Power Management DIMM WrCas Energy: DIMM1_WR_ENERGY: This register defines the energy contribution of a write CAS command. chipset: 79h MCHBAR: PM—Power Management DIMM WrCas Energy: DIMM0_WR_ENERGY: This register defines the energy contribution of a write CAS command. chipset: MCHBAR: MAD—Address decoder Channel configuration register: This register defines which channel is assigned to be channel A, channel B and channel C according to the rule: size(A) >= size (B) >= size(C). Since the processor implements only two channels, channel C is always channel 2, and its size is always 0 chipset: 1h MCHBAR: MAD—Address decoder Channel configuration register: LPDDR LPDDR - Indicate that LPDDR devices are connected used on the system rather than DDR3 devices.: chipset: Channel 2 MCHBAR: MAD—Address decoder Channel configuration register: CH_C CH_C - defines the smallest channel: chipset: Channel 1 MCHBAR: MAD—Address decoder Channel configuration register: CH_B CH_B - defines the mid-size channel: chipset: Channel 0 MCHBAR: MAD—Address decoder Channel configuration register: CH_A CH_A - defines the largest channel: chipset: MCHBAR: MAD—Address decode channel 0: This register defines channel characteristics - number of DIMMs, number of ranks, size, ECC, interleave options and ECC options chipset: 20 MCHBAR: MAD—Address decode channel 0: HORIAddr High Order Rank Interleave Address. Specifies which DIMM address bit 20-27 to use as the rank interleave bit: chipset: off MCHBAR: MAD—Address decode channel 0: HORI High Order Rank Interleave. High Order Rank Interleave (HORI) is mutually exclusive with Rank Interleave (RI) chipset: No ECC active in the channel. MCHBAR: MAD—Address decode channel 0: ECC ECC configuration in the channel: Note: This field must be programmed identically for all populated channels. chipset: on MCHBAR: MAD—Address decode channel 0: Enh_Interleave Enhanced interleave mode: chipset: on MCHBAR: MAD—Address decode channel 0: RI Rank Interleave: chipset: Other than X16 chips MCHBAR: MAD—Address decode channel 0: DBW DBW: DIMM B width of DDR chips chipset: Other than X16 chips MCHBAR: MAD—Address decode channel 0: DAW DAW: DIMM A width of DDR chips chipset: single rank MCHBAR: MAD—Address decode channel 0: DBNOR DIMM B number of ranks: chipset: dual rank MCHBAR: MAD—Address decode channel 0: DANOR DIMM A number of ranks: chipset: DIMM 0 MCHBAR: MAD—Address decode channel 0: DAS Selects which of the DIMMs is DIMM A - should be the larger DIMM: chipset: 0 raw: MCHBAR: MAD—Address decode channel 0: DIMM_B_Size Size of DIMM B in 256 MB multiples chipset: 8 raw: MCHBAR: MAD—Address decode channel 0: DIMM_A_Size Size of DIMM A in 256 MB multiples chipset: 0 MBs: MCHBAR: MAD—Address decode channel 0: DIMM_B_Size Size of DIMM B in 256 MB multiples chipset: 2048 MBs: MCHBAR: MAD—Address decode channel 0: DIMM_A_Size Size of DIMM A in 256 MB multiples chipset: MCHBAR: MAD—Address decode channel 1: This register defines channel characteristics - number of DIMMs, number of ranks, size, ECC, interleave options and ECC options chipset: 20 MCHBAR: MAD—Address decode channel 1: HORIAddr High Order Rank Interleave Address. Specifies which DIMM address bit 20-27 to use as the rank interleave bit: chipset: off MCHBAR: MAD—Address decode channel 1: HORI High Order Rank Interleave. High Order Rank Interleave (HORI) is mutually exclusive with Rank Interleave (RI) chipset: No ECC active in the channel. MCHBAR: MAD—Address decode channel 1: ECC ECC configuration in the channel: Note: This field must be programmed identically for all populated channels. chipset: on MCHBAR: MAD—Address decode channel 1: Enh_Interleave Enhanced interleave mode: chipset: on MCHBAR: MAD—Address decode channel 1: RI Rank Interleave: chipset: Other than X16 chips MCHBAR: MAD—Address decode channel 1: DBW DBW: DIMM B width of DDR chips chipset: Other than X16 chips MCHBAR: MAD—Address decode channel 1: DAW DAW: DIMM A width of DDR chips chipset: single rank MCHBAR: MAD—Address decode channel 1: DBNOR DIMM B number of ranks: chipset: dual rank MCHBAR: MAD—Address decode channel 1: DANOR DIMM A number of ranks: chipset: DIMM 0 MCHBAR: MAD—Address decode channel 1: DAS Selects which of the DIMMs is DIMM A - should be the larger DIMM: chipset: 0 raw: MCHBAR: MAD—Address decode channel 1: DIMM_B_Size Size of DIMM B in 256 MB multiples chipset: 8 raw: MCHBAR: MAD—Address decode channel 1: DIMM_A_Size Size of DIMM A in 256 MB multiples chipset: 0 MBs: MCHBAR: MAD—Address decode channel 1: DIMM_B_Size Size of DIMM B in 256 MB multiples chipset: 2048 MBs: MCHBAR: MAD—Address decode channel 1: DIMM_A_Size Size of DIMM A in 256 MB multiples chipset: MCHBAR: PM—Self refresh config. register: Self refresh mode control register - defines if and when DDR can go into SR: chipset: 1 MCHBAR: PM—Self refresh config. register: SR_Enable enables or disables self-refresh mechanism. In order to allow SR, both SREF_en bit should be set and SREF_exit signal should be cleared. PM_SREF_config may be updated in run-time chipset: 200h MCHBAR: PM—Self refresh config. register: Idle_timer This value is used when the SREF_enable field is set. It defines the number of cycles that there should not be any transaction in order to enter self-refresh. It is programmable from 512 to 64K-1. In DCLK=800 it determines time of up to 82 us. This parameter has been adjusted to protect ODTLoff + 1 to MRS command timing. As part of the bug fix for bug 3138064/3538082 the minimum time has been increased to 512. See the bug for details. chipset: MCHBAR: DDR—DDR_PTM_CTL: Mode control bits for DDR power and thermal management features. chipset: 1 MCHBAR: DDR—DDR_PTM_CTL: DISABLE_DRAM_TS: When this bit is zero and MAD_CHNL.LPDDR=1, pcode will use DDR MR4 for DIMM thermal status purposes. Otherwise, pcode will ignore MR4 data and use the legacy CLTM/OLTM/EXTTS algorithms for computing DIMM thermal status. chipset: 0 MCHBAR: DDR—DDR_PTM_CTL: PDWN_CONFIG_CTL: This bit determined whether BIOS or pcode will control DDR powerdown modes and idle counter (via programming the PM_PDWN_config regs in iMC). When clear, pcode will manage the modes based on either core P-states or IA32_ENERGY_PERFORMANCE_BIAS MSR value (when enabled). When set, BIOS is in control of DDR CKE mode and idle timer value, and pcode algorithm does not run. chipset: 1 MCHBAR: DDR—DDR_PTM_CTL: LOCK_PTM_REGS_PCU: When set, several PCU registers related to DDR power/ thermal management all become unwritable (writes will be silently ignored). List of registered locked by this bit is: DDR_WARM_THRESHOLD_CH*, DDR_HOT_THRESHOLD_CH*, DDR_WARM_BUDGET_CH*, DDR_HOT_BUDGET_CH*, (note that RAPL regs, such as RAPL_LIMIT, are NOT included as those have separate lock bit). Note that BIOS should complete its writes to all of the locked registers prior to setting this bit, since it can only be reset via uncore reset. chipset: 0 MCHBAR: DDR—DDR_PTM_CTL: EXTTS_ENABLE When clear (default), pcode ignores the EXTTS (external thermal status) indication which is obtained from the PCH (via PM_SYNC). When set, the value from EXTTS is used only when it is hotter than the thermal status reported by OLTM/CLTM algorithm (or used all of the time if neither of those modes is enabled). chipset: 0 MCHBAR: DDR—DDR_PTM_CTL: REFRESH_2X_MODE: These bits are read by reset pcode and later broadcast (together with the thermal status) into the iMC cregs that control 2x refresh modes. When DRAM is hot, it accumulates bits errors more quickly. The iMC refresh mechanism is how those errors get prevented and corrected (using ECC). Thus in order to maintain an acceptable overall error rate, the refresh rate needs to increase with temperature. This is a very coarse grain mechanism for accomplishing that. A value of 00 means the iMC 2x refresh is disabled. A value of 01 means that the iMC will enable 2x refresh whenever thermal status is WARM or HOT. A value of 10 means the iMC will enable 2x refresh only when HOT. The value 11 is illegal, and will trigger an assertion in the iMC (BIOS should not do this). This field is ignored for LPDDR when DISABLE_DRAM_TS is zero, in which case refresh rates in the MC are controlled by MR4 coming directly from DIMMs. chipset: 1 MCHBAR: DDR—DDR_PTM_CTL: CLTM_ENABLE A value of 1 means CLTM (Closed Loop Thermal Management) pcode algorithm will be used to compute the memory thermal status (which will be written to the iMC). Note that OLTM and CLTM modes are mutex, so if both OLTM_ENABLE and CLTM_ENABLE are set, the OLTM_ENABLE will be ignored and CTLM mode will be active. BIOS should enable CLTM whenever DIMM thermal sensor data is available and memory thermal management is desired. chipset: 0 MCHBAR: DDR—DDR_PTM_CTL: OLTM_ENABLE A value of 1 means OLTM (Open Loop Thermal Management) pcode algorithm will be used to compute the memory thermal status (which will be written to the iMC). Note that OLTM and CLTM modes are mutex, so if both OLTM_ENABLE and CLTM_ENABLE are set, the OLTM_ENABLE will be ignored and CTLM mode will be active. BIOS should enable CLTM whenever DIMM thermal sensor data is not available, but memory thermal management is desired. Obviously lack of real temperature data means this mode will be somewhat conservative, and may result in the iMC throttling more often than necessary. Thus for perf reasons CLTM is preferred on systems with available DIMM thermal sensor data. chipset: MCHBAR: DRAM—DRAM_ENERGY_SCALEFACTOR: Defines the base energy unit for DDR energy values in iMC command energy config regs, iMC rank energy counters (used for OLTM and Memory RAPL), OLTM thresholds, etc. chipset: 29.1pJ MCHBAR: DRAM—DRAM_ENERGY_SCALEFACTOR: SCALEFACTOR Defines the base DDR energy unit of 2^(-30-scalefactor) Joules. The default reset value is 3 = 116.4pJ. The values are defined as follows: chipset: MCHBAR: DRAM—DRAM_RAPL_CHANNEL_POWER_FLOOR: Defines the minimum required power consumption of each DDR channel, in order to satisfy minimum memory bandwidth requirements for the platform. DDR RAPL should never throttle below the levels defined here. It is the responsibility of BIOS to comprehend the power consumption on each channel in order to write meaningful values into this register. chipset: 4 MCHBAR: DRAM—DRAM_RAPL_CHANNEL_POWER_FLOOR: CH1 Minimum power level (in format of 5.3 W) used to clip DDR RAPL power budget for channel 1.: chipset: 4 MCHBAR: DRAM—DRAM_RAPL_CHANNEL_POWER_FLOOR: CH0 Minimum power level (in format of 5.3 W) used to clip DDR RAPL power budget for channel 0.: chipset: MCHBAR: DDR—DDR_THERM_PERDIMM_STATUS: Per-DIMM thermal status values. The encoding of each DIMM thermal status is the same: chipset: COLD MCHBAR: DDR—DDR_THERM_PERDIMM_STATUS: CH1_DIMM1 Thermal Status for Channel 1, DIMM1 chipset: COLD MCHBAR: DDR—DDR_THERM_PERDIMM_STATUS: CH1_DIMM0 Thermal Status for Channel 1, DIMM0 chipset: COLD MCHBAR: DDR—DDR_THERM_PERDIMM_STATUS: CH0_DIMM1 Thermal Status for Channel 0, DIMM1 chipset: COLD MCHBAR: DDR—DDR_THERM_PERDIMM_STATUS: CH0_DIMM0 Thermal Status for Channel 0, DIMM0 chipset: MCHBAR: DDR—DDR_WARM_THRESHOLD_CH0: Per-DIMM temp/power thresholds used for CLTM/OLTM thermal status computation. These values can impact iMC throttling and memory thermal interrrupts. chipset: 255 MCHBAR: DDR—DDR_WARM_THRESHOLD_CH0: DIMM1 WARM_THRESHOLD for DIMM1 on this channel. chipset: 255 MCHBAR: DDR—DDR_WARM_THRESHOLD_CH0: DIMM0 WARM_THRESHOLD for DIMM0 on this channel. chipset: MCHBAR: DDR—DDR_WARM_THRESHOLD_CH1: Per-DIMM temp/power thresholds used for CLTM/OLTM thermal status computation. These values can impact iMC throttling and memory thermal interrrupts. chipset: 255 MCHBAR: DDR—DDR_WARM_THRESHOLD_CH1: DIMM1 WARM_THRESHOLD for DIMM1 on this channel. chipset: 255 MCHBAR: DDR—DDR_WARM_THRESHOLD_CH1: DIMM0 WARM_THRESHOLD for DIMM0 on this channel. chipset: MCHBAR: DDR—DDR_HOT_THRESHOLD_CH0: Per-DIMM temp/power thresholds used for CLTM/OLTM thermal status computation. These values can impact iMC throttling and memory thermal interrrupts. chipset: 255 MCHBAR: DDR—DDR_HOT_THRESHOLD_CH0: DIMM1 HOT_THRESHOLD for DIMM1 on this channel. chipset: 255 MCHBAR: DDR—DDR_HOT_THRESHOLD_CH0: DIMM0 HOT_THRESHOLD for DIMM0 on this channel. chipset: MCHBAR: DDR—DDR_HOT_THRESHOLD_CH1: Per-DIMM temp/power thresholds used for CLTM/OLTM thermal status computation. These values can impact iMC throttling and memory thermal interrrupts. chipset: 255 MCHBAR: DDR—DDR_HOT_THRESHOLD_CH1: DIMM1 HOT_THRESHOLD for DIMM1 on this channel. chipset: 255 MCHBAR: DDR—DDR_HOT_THRESHOLD_CH1: DIMM0 HOT_THRESHOLD for DIMM0 on this channel. chipset: MCHBAR: DDR—DDR_THERM_INTERRUPT_CONFIG: Enable bits and policy-free thresholds used for controlling memory thermal interrupt generation. chipset: 0 MCHBAR: DDR—DDR_THERM_INTERRUPT_CONFIG: POLICY_FREE_THRESHOLD2: A threshold temperature value used only for interrupt generation. No iMC throttling or other actions should be directly affected by this value. This only works when CLTM is enabled. This is an 8-bit unsigned value in 7.1 format, 0.5C increment. THRESHOLD1 and THRESHOLD2 values and enables are fully independent from each other. chipset: 0 MCHBAR: DDR—DDR_THERM_INTERRUPT_CONFIG: POLICY_FREE_THRESHOLD1: A threshold temperature value used only for interrupt generation. No iMC throttling or other actions should be directly affected by this value. This only works when CLTM is enabled. This is an 8-bit unsigned value in 7.1 format, 0.5C increment. THRESHOLD1 and THRESHOLD2 values and enables are fully independent from each other. chipset: 0 MCHBAR: DDR—DDR_THERM_INTERRUPT_CONFIG: ENABLE_THRESHOLD2_INTERRUPT: When set, interrupts will be generated on both rising and falling transition of the hottest absolute DIMM temperature across the POLICY_FREE_THRESHOLD2 value. This interrupt will never get triggered by pcode in cases where CLTM is not enabled (i.e. does not work with OLTM). THRESHOLD1 and THRESHOLD2 values and enables are fully independent from each other. chipset: 0 MCHBAR: DDR—DDR_THERM_INTERRUPT_CONFIG: ENABLE_THRESHOLD1_INTERRUPT: When set, interrupts will be generated on both rising and falling transition of the hottest absolute DIMM temperature across the POLICY_FREE_THRESHOLD1 value. This interrupt will never get triggered by pcode in cases where CLTM is not enabled (i.e. does not work with OLTM). THRESHOLD1 and THRESHOLD2 values and enables are fully independent from each other. chipset: 0 MCHBAR: DDR—DDR_THERM_INTERRUPT_CONFIG: ENABLE_OOS_TEMP_INTERRUPT: When set, interrupts will be generated on a rising transition of hottest MR4 to 3'b111. This interrupt will never get triggered by pcode in cases where MAD_CHNL.LPDDR is zero or DISABLE_DRAM_TS is set. chipset: 0 MCHBAR: DDR—DDR_THERM_INTERRUPT_CONFIG: ENABLE_2X_REFRESH_INTERRUPT: When set, interrupts will be generated on a rising transition of the hottest DIMM thermal status across whichever threshold 2x refresh is configured for (WARM_THRESHOLD, HOT_THRESHOLD, or never, depending on DDR_PTM_CTL.REFRESH_2X_MODE). This interrupt will never be triggered by pcode in cases where 2X refresh is disabled OR when no thermal status updates are being performed because CLTM, OLTM, and EXTTS are all disabled. In the case of LPDDR when DISABLE_DRAM_TS is zero, MR4 is used for refresh rate control and this interrupt still exists but its name becomes slightly misleading... in that case it is triggered whenever MR4 changes such that DIMM refresh rate has crossed the boundary (in either direction) between 1x or lower refresh rate, and higher than 1x refresh rate. LPDDR might go above the 2x refresh rate and still generate this interrupt, for example. chipset: 0 MCHBAR: DDR—DDR_THERM_INTERRUPT_CONFIG: ENABLE_HOT_INTERRUPT: When set, interrupts will be generated on a rising transition of the hottest DIMM thermal status from WARM to HOT (i.e. rise to or above HOT_THRESHOLD). This interrupt will never get triggered by pcode in cases where CLTM, OLTM, and EXTTS are all disabled. chipset: 0 MCHBAR: DDR—DDR_THERM_INTERRUPT_CONFIG: ENABLE_WARM_INTERRUPT: When set, interrupts will be generated on a rising transition of the hottest DIMM thermal status from COLD to WARM (i.e. rise to or above WARM_THRESHOLD). This interrupt will never get triggered by pcode in cases where CLTM, OLTM, and EXTTS are all disabled. chipset: MCHBAR: PACKAGE—PACKAGE_THERM_MARGIN: Temperature margin in PECI temperature counts from the thermal profile specification. Platform fan control SW is expected to read therm_margin value to control fan or blower speed. chipset: 2040h raw: MCHBAR: PACKAGE—PACKAGE_THERM_MARGIN: THERM_MARGIN: Temperature margin in PECI temperature counts from the thermal profile specification. THERM_MARGIN is in 2's complement format (8.8 format where MSB equals 1 Sign bit + 7 bits of integer temperature value and the LSB equals 8 precison bits of temperature value). A value of zero indicates the hottest CPU die temperature is on the thermal profile line. A negative value indicates gap to the thermal profile that platform SW should increase cooling capacity. A sustained negative value should be avoided as it may impact part reliability. chipset: 32 conv: MCHBAR: PACKAGE—PACKAGE_THERM_MARGIN: THERM_MARGIN: Temperature margin in PECI temperature counts from the thermal profile specification. THERM_MARGIN is in 2's complement format (8.8 format where MSB equals 1 Sign bit + 7 bits of integer temperature value and the LSB equals 8 precison bits of temperature value). A value of zero indicates the hottest CPU die temperature is on the thermal profile line. A negative value indicates gap to the thermal profile that platform SW should increase cooling capacity. A sustained negative value should be avoided as it may impact part reliability. chipset: MCHBAR: DDR—DDR_DIMM_TEMPERATURE_CH0: Per-DIMM temperature values. chipset: 31 MCHBAR: DDR—DDR_DIMM_TEMPERATURE_CH0: DIMM1 Temperature of DIMM1 on this channel. chipset: 31 MCHBAR: DDR—DDR_DIMM_TEMPERATURE_CH0: DIMM0 Temperature of DIMM0 on this channel. chipset: MCHBAR: DDR—DDR_DIMM_TEMPERATURE_CH1: Per-DIMM temperature values. chipset: 31 MCHBAR: DDR—DDR_DIMM_TEMPERATURE_CH1: DIMM1 Temperature of DIMM1 on this channel. chipset: 31 MCHBAR: DDR—DDR_DIMM_TEMPERATURE_CH1: DIMM0 Temperature of DIMM0 on this channel. chipset: MCHBAR: DDR—DDR_THROTTLE_DURATION_CH0: Per-DIMM throttle duration counters. These accumulate the duration (in absolute wall clock time) that the iMC rank throttlers have been blocking memory traffic due to OLTM/CLTM/EXTTS thermal status. Note that RAPL throttling is done at the channel level, and thus is NOT included in these values. chipset: 0 raw: MCHBAR: DDR—DDR_THROTTLE_DURATION_CH0: DIMM1 Throttle duration of DIMM 1 on this channel, in units of 1/1024 seconds. chipset: 0 raw: MCHBAR: DDR—DDR_THROTTLE_DURATION_CH0: DIMM0 Throttle duration of DIMM 0 on this channel, in units of 1/1024 seconds. chipset: 0 Secs: MCHBAR: DDR—DDR_THROTTLE_DURATION_CH0: DIMM1 Throttle duration of DIMM 1 on this channel, in units of 1/1024 seconds. chipset: 0 Secs: MCHBAR: DDR—DDR_THROTTLE_DURATION_CH0: DIMM0 Throttle duration of DIMM 0 on this channel, in units of 1/1024 seconds. chipset: MCHBAR: DDR—DDR_THROTTLE_DURATION_CH1: Per-DIMM throttle duration counters. These accumulate the duration (in absolute wall clock time) that the iMC rank throttlers have been blocking memory traffic due to OLTM/CLTM/EXTTS thermal status. Note that RAPL throttling is done at the channel level, and thus is NOT included in these values. chipset: 0 raw: MCHBAR: DDR—DDR_THROTTLE_DURATION_CH1: DIMM1 Throttle duration of DIMM 1 on this channel, in units of 1/1024 seconds. chipset: 0 raw: MCHBAR: DDR—DDR_THROTTLE_DURATION_CH1: DIMM0 Throttle duration of DIMM 0 on this channel, in units of 1/1024 seconds. chipset: 0 Secs: MCHBAR: DDR—DDR_THROTTLE_DURATION_CH1: DIMM1 Throttle duration of DIMM 1 on this channel, in units of 1/1024 seconds. chipset: 0 Secs: MCHBAR: DDR—DDR_THROTTLE_DURATION_CH1: DIMM0 Throttle duration of DIMM 0 on this channel, in units of 1/1024 seconds. chipset: MCHBAR: DDR—DDR_WARM_BUDGET_CH0: Per-DIMM power budget for MC thermal throttling when thermal status is WARM. chipset: 255 MCHBAR: DDR—DDR_WARM_BUDGET_CH0: DIMM1 WARM_BUDGET for DIMM1 on this channel. chipset: 255 MCHBAR: DDR—DDR_WARM_BUDGET_CH0: DIMM0 WARM_BUDGET for DIMM0 on this channel. chipset: MCHBAR: DDR—DDR_WARM_BUDGET_CH1: Per-DIMM power budget for MC thermal throttling when thermal status is WARM. chipset: 255 MCHBAR: DDR—DDR_WARM_BUDGET_CH1: DIMM1 WARM_BUDGET for DIMM1 on this channel. chipset: 255 MCHBAR: DDR—DDR_WARM_BUDGET_CH1: DIMM0 WARM_BUDGET for DIMM0 on this channel. chipset: MCHBAR: DDR—DDR_HOT_BUDGET_CH0: Per-DIMM power budget for MC thermal throttling when thermal status is HOT. chipset: 255 MCHBAR: DDR—DDR_HOT_BUDGET_CH0: DIMM1 HOT_BUDGET for DIMM1 on this channel. chipset: 255 MCHBAR: DDR—DDR_HOT_BUDGET_CH0: DIMM0 HOT_BUDGET for DIMM0 on this channel. chipset: MCHBAR: DDR—DDR_HOT_BUDGET_CH1: Per-DIMM power budget for MC thermal throttling when thermal status is HOT. chipset: 255 MCHBAR: DDR—DDR_HOT_BUDGET_CH1: DIMM1 HOT_BUDGET for DIMM1 on this channel. chipset: 255 MCHBAR: DDR—DDR_HOT_BUDGET_CH1: DIMM0 HOT_BUDGET for DIMM0 on this channel. chipset: MCHBAR: DRAM—DRAM_POWER_LIMIT: Allows software to set power limits for the DRAM domain and measurement attributes associated with each limit. chipset: not locked MCHBAR: DRAM—DRAM_POWER_LIMIT: LOCKED When set, this entire register becomes read-only. This bit will typically be set by BIOS during boot. chipset: 1 MCHBAR: DRAM—DRAM_POWER_LIMIT: LIMIT2_TIME_WINDOW_X: Power Limit[1] time window X value, for DDR domain. Actual time_window for RAPL is: (1/1024 seconds) * (1+ (x/4)) * (2^y) chipset: 10 MCHBAR: DRAM—DRAM_POWER_LIMIT: LIMIT2_TIME_WINDOW_Y: Power Limit[1] time window Y value, for DDR domain. Actual time_window for RAPL is: (1/1024 seconds) * (1+ (x/4)) * (2^y) chipset: 1.25 Secs: MCHBAR: DRAM—DRAM_POWER_LIMIT: LIMIT2_TIME_WINDOW: Power Limit[1] time window calculated value, for DDR domain. Actual time_window for RAPL is: (1/1024 seconds) * (1+ (x/4)) * (2^y) chipset: 0 MCHBAR: DRAM—DRAM_POWER_LIMIT: LIMIT2_ENABLE: Power Limit[1] enable bit for DDR domain. chipset: 222 Raw: MCHBAR: DRAM—DRAM_POWER_LIMIT: LIMIT2_POWER Power Limit[1] for DDR domain. Units=Watts, Format=11.3, Resolution=0.125W, Range=0-2047.875W. chipset: 27.75 Watts: MCHBAR: DRAM—DRAM_POWER_LIMIT: LIMIT2_POWER Power Limit[1] for DDR domain. Units=Watts, Format=11.3, Resolution=0.125W, Range=0-2047.875W. chipset: 3 MCHBAR: DRAM—DRAM_POWER_LIMIT: LIMIT1_TIME_WINDOW_X: Power Limit[0] time window X value, for DDR domain. Actual time_window for RAPL is: (1/1024 seconds) * (1+ (x/4)) * (2^y) chipset: 14 MCHBAR: DRAM—DRAM_POWER_LIMIT: LIMIT1_TIME_WINDOW_Y: Power Limit[0] time window Y value, for DDR domain. Actual time_window for RAPL is: (1/1024 seconds) * (1+ (x/4)) * (2^y) chipset: 28 Secs: MCHBAR: DRAM—DRAM_POWER_LIMIT: LIMIT1_TIME_WINDOW: Power Limit[0] time window calculated value, for DDR domain. Actual time_window for RAPL is: (1/1024 seconds) * (1+ (x/4)) * (2^y) chipset: 1 MCHBAR: DRAM—DRAM_POWER_LIMIT: LIMIT1_ENABLE: Power Limit[0] enable bit for DDR domain. chipset: 145 Raw: MCHBAR: DRAM—DRAM_POWER_LIMIT: LIMIT1_POWER: Power Limit[0] for DDR domain. Units=Watts, Format=11.3, Resolution=0.125W, Range=0-2047.875W chipset: 18.125 Watts: MCHBAR: DRAM—DRAM_POWER_LIMIT: LIMIT1_POWER: Power Limit[0] for DDR domain. Units=Watts, Format=11.3, Resolution=0.125W, Range=0-2047.875W chipset: MCHBAR: DRAM—DRAM_ENERGY_STATUS: Accumulates the energy consumed by the DIMMs (summed across all channels). chipset: 1339614 Raw: MCHBAR: DRAM—DRAM_ENERGY_STATUS: JOULES_CONSUMED: Total Joules of energy consumed by all DIMMs: Format= 18.14, Resolution = ~61uJ, Range = 0 to 2.62e5 J. chipset: 81.7165 Joules: MCHBAR: DRAM—DRAM_ENERGY_STATUS: JOULES_CONSUMED: Total Joules of energy consumed by all DIMMs: Format= 18.14, Resolution = ~61uJ, Range = 0 to 2.62e5 J. chipset: MCHBAR: DRAM—DRAM_RAPL_PERF_STATUS: Memory RAPL performance excursion counter. This register can report the performance impact of power limiting. chipset: 0 Raw: MCHBAR: DRAM—DRAM_RAPL_PERF_STATUS: DURATION: Throttle duration due to RAPL (sum across all channels), in units of 1/1024 seconds. This data can serve as a proxy for the potential performance impacts of RAPL on memory accesses. This is a real time accumulator that is based on iMC counters at QCLK granularity, thus this register is more accurate than PACKAGE_RAPL_PERF_STATUS. chipset: 0 Secs: MCHBAR: DRAM—DRAM_RAPL_PERF_STATUS: DURATION: Throttle duration due to RAPL (sum across all channels), in units of 1/1024 seconds. This data can serve as a proxy for the potential performance impacts of RAPL on memory accesses. This is a real time accumulator that is based on iMC counters at QCLK granularity, thus this register is more accurate than PACKAGE_RAPL_PERF_STATUS. chipset: MCHBAR: PACKAGE—PACKAGE_RAPL_PERF_STATUS: Package RAPL Performance Status Register. This register provides information on the performance impact of the RAPL power limit and indicates the duration for processor went below the requested P-state due to package power constraint. chipset: 59 Raw: MCHBAR: PACKAGE—PACKAGE_RAPL_PERF_STATUS: COUNTS: Counter of the time units within which RAPL was limiting Pstates: If limitation occurred anywhere within the time window of 1/1024 seconds, the count will be incremented (limitation on accuracy). This data can serve as a proxy for the potential performance impacts of RAPL on cores performance. chipset: 0.0576172 Secs: MCHBAR: PACKAGE—PACKAGE_RAPL_PERF_STATUS: COUNTS: Counter of the time units within which RAPL was limiting Pstates: If limitation occurred anywhere within the time window of 1/1024 seconds, the count will be incremented (limitation on accuracy). This data can serve as a proxy for the potential performance impacts of RAPL on cores performance. chipset: MCHBAR: PRIMARY—PRIMARY_PLANE_TURBO_POWER_POLICY: The PRIMARY_PLANE_TURBO_POWER_POLICY and SECONDARY_PLANE_TURBO_POWER_POLICY are used together to balance the power budget betwen the two power planes. The power plane with the higher policy will get a higher priority. The default values for these registers give a higher priority to the secondary power plane. chipset: 9 MCHBAR: PRIMARY—PRIMARY_PLANE_TURBO_POWER_POLICY: PRIPTP Priority Level. A higher number implies a higher priority. chipset: MCHBAR: SECONDARY—SECONDARY_PLANE_TURBO_POWER_POLICY: The PRIMARY_PLANE_TURBO_POWER_POLICY and SECONDARY_PLANE_TURBO_POWER_POLICY are used together to balance the power budget betwen the two power planes. The power plane with the higher policy will get a higher priority. The default values for these registers give a higher priority to the secondary power plane. chipset: 13 MCHBAR: SECONDARY—SECONDARY_PLANE_TURBO_POWER_POLICY: SECPTP: Priority Level. A higher number implies a higher priority. chipset: MCHBAR: MSR—MSR_RAPL_POWER_UNIT: Defines units for calculating SKU power and timing parameters. chipset: 10 Raw: MCHBAR: MSR—MSR_RAPL_POWER_UNIT: TIME_UNIT: Time Units used for power control registers. The actual unit value is calculated by 1 s / Power(2,TIME_UNIT). The default value of Ah corresponds to 976 usec. chipset: 0.000976563 Secs: MCHBAR: MSR—MSR_RAPL_POWER_UNIT: TIME_UNIT: Time Units used for power control registers. The actual unit value is calculated by 1 s / Power(2,TIME_UNIT). The default value of Ah corresponds to 976 usec. chipset: 14 Raw: MCHBAR: MSR—MSR_RAPL_POWER_UNIT: ENERGY_UNIT: Energy Units used for power control registers. The actual unit value is calculated by 1 J / Power(2,ENERGY_UNIT). The default value of 14 corresponds to Ux.14 number. chipset: 6.10352e-005 Joules: MCHBAR: MSR—MSR_RAPL_POWER_UNIT: ENERGY_UNIT: Energy Units used for power control registers. The actual unit value is calculated by 1 J / Power(2,ENERGY_UNIT). The default value of 14 corresponds to Ux.14 number. chipset: 3 Raw: MCHBAR: MSR—MSR_RAPL_POWER_UNIT: PWR_UNIT Power Units used for power control registers. The actual unit value is calculated by 1 W / Power(2,PWR_UNIT). The default value of 0011b corresponds to 1/8 W. chipset: 0.125 Watts: MCHBAR: MSR—MSR_RAPL_POWER_UNIT: PWR_UNIT Power Units used for power control registers. The actual unit value is calculated by 1 W / Power(2,PWR_UNIT). The default value of 0011b corresponds to 1/8 W. chipset: MCHBAR: PACKAGE—PACKAGE_POWER_SKU: Defines allowed SKU power and timing parameters. chipset: 0 Raw: MCHBAR: PACKAGE—PACKAGE_POWER_SKU: PKG_MAX_WIN_X: The maximal time window allowed for the SKU. Higher values will be clamped to this value. x = PKG_MAX_WIN[54:53] y = PKG_MAX_WIN[52:48] The timing interval window is Floating Point number given by 1.x * power(2,y). The unit of measurement is defined in PACKAGE_POWER_SKU_UNIT_MSR[TIME_UNIT]. chipset: 0 Raw: MCHBAR: PACKAGE—PACKAGE_POWER_SKU: PKG_MAX_WIN_Y: The maximal time window allowed for the SKU. Higher values will be clamped to this value. x = PKG_MAX_WIN[54:53] y = PKG_MAX_WIN[52:48] The timing interval window is Floating Point number given by 1.x * power(2,y). The unit of measurement is defined in PACKAGE_POWER_SKU_UNIT_MSR[TIME_UNIT]. chipset: 0 Secs: MCHBAR: PACKAGE—PACKAGE_POWER_SKU: PKG_MAX_WIN: The maximal time window allowed for the SKU. Higher values will be clamped to this value. x = PKG_MAX_WIN[54:53] y = PKG_MAX_WIN[52:48] The timing interval window is Floating Point number given by 1.x * power(2,y). The unit of measurement is defined in PACKAGE_POWER_SKU_UNIT_MSR[TIME_UNIT]. chipset: 0 Raw: MCHBAR: PACKAGE—PACKAGE_POWER_SKU: PKG_MAX_PWR: The maximal package power setting allowed for the SKU. Higher values will be clamped to this value. The maximum setting is typical (not guaranteed). The units for this value are defined in PACKAGE_POWER_SKU_MSR[PWR_UNIT]. chipset: 0 Watts: MCHBAR: PACKAGE—PACKAGE_POWER_SKU: PKG_MAX_PWR: The maximal package power setting allowed for the SKU. Higher values will be clamped to this value. The maximum setting is typical (not guaranteed). The units for this value are defined in PACKAGE_POWER_SKU_MSR[PWR_UNIT]. chipset: 0 Raw: MCHBAR: PACKAGE—PACKAGE_POWER_SKU: PKG_MIN_PWR The minimal package power setting allowed for this part. Lower values will be clamped to this value. The minimum setting is typical (not guaranteed). The units for this value are defined in PACKAGE_POWER_SKU_MSR[PWR_UNIT]. chipset: 0 Watts: MCHBAR: PACKAGE—PACKAGE_POWER_SKU: PKG_MIN_PWR The minimal package power setting allowed for this part. Lower values will be clamped to this value. The minimum setting is typical (not guaranteed). The units for this value are defined in PACKAGE_POWER_SKU_MSR[PWR_UNIT]. chipset: PACKAGE—PACKAGE_ENERGY_STATUS: Package energy consumed by the entire CPU (including IA, Integrated Graphics and Uncore). The counter will wrap around and continue counting when it reaches its limit. The energy status is reported in units which are defined in PACKAGE_POWER_SKU_UNIT_MSR[ENERGY_UNIT]. chipset: 30079025 Raw: PACKAGE—PACKAGE_ENERGY_STATUS: DATA: Energy Value chipset: 1835.88 Joules: PACKAGE—PACKAGE_ENERGY_STATUS: DATA: Energy Value chipset: MCHBAR: GT—GT_PERF_STATUS: P-state encoding for the Secondary Power Plane's current PLL frequency and the current VID. chipset: 12 Raw: MCHBAR: GT—GT_PERF_STATUS: RP_STATE_RATIO: Ratio of the current RP-state chipset: 1200 MHz: MCHBAR: GT—GT_PERF_STATUS: RP_STATE_RATIO: Ratio of the current RP-state chipset: 0 MCHBAR: GT—GT_PERF_STATUS: RP_STATE_VOLTAGE: Voltage of the current RP-state.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Patrick Fay (Intel) wrote:

What is your CPU's cpuid brand string? The string like on my laptop 'Intel(R) Core(TM) i5-3427U CPU @ 1.80GHz'.

This will tell us the architecture and target system type (client, server, etc) for the chip.

Pat

Thanks Pat

I ran cat /proc/cpuinfo and got this

processor : 0 vendor_id : GenuineIntel cpu family : 6 model : 42 model name : Intel(R) Core(TM) i7-2600 CPU @ 3.40GHz stepping : 7 cpu MHz : 3401.000 cache size : 8192 KB physical id : 0 siblings : 8 core id : 0 cpu cores : 4 apicid : 0 initial apicid : 0 fdiv_bug : no hlt_bug : no f00f_bug : no coma_bug : no fpu : yes fpu_exception : yes cpuid level : 13 wp : yes flags : fpu vme de pse tsc msr pae mce cx8 apic sep mtrr pge mca cmov pat pse36 clflush dts acpi mmx fxsr sse sse2 ss ht tm pbe nx rdtscp lm constant_tsc arch_perfmon pebs bts xtopology nonstop_tsc aperfmperf pni pclmulqdq dtes64 monitor ds_cpl vmx smx est tm2 ssse3 cx16 xtpr pdcm pcid sse4_1 sse4_2 x2apic popcnt tsc_deadline_timer aes xsave avx lahf_lm ida arat epb xsaveopt pln pts dts tpr_shadow vnmi flexpriority ept vpid bogomips : 6784.27 clflush size : 64 cache_alignment : 64 address sizes : 36 bits physical, 48 bits virtual power management:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

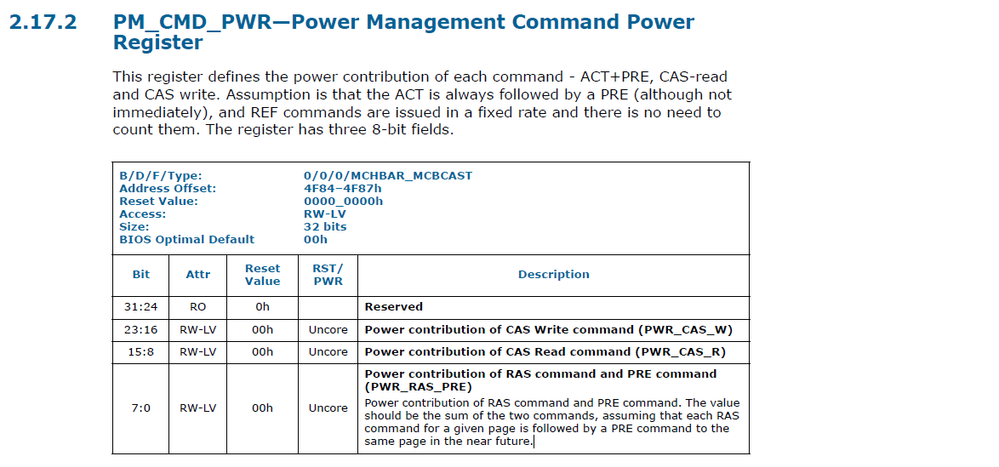

You have a Sandybridge-based CPU. The system doesn't have RAPL DRAM MSRs. There is a MCHBAR-based register in the datasheet that has some of what you'd need to measure DRAM energy but that is all I could find.

The register defines a power contribution for certain DRAM operations. I don't know what the unit is or if the register is even non-zero on your system. And you'd still have to measure the 'ACT+PRE, CAS-read and CAS write commands (using VTune? I don't know if it measures these commands on your system).

So there isn't a very easy way to measure DRAM power on your system and, if you get it working, you would have DRAM power for the system as a whole... you wouldn't be able to attribute the power to a particular process (unless the process is only thing using DRAM).

Pat

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page