- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Sir/madam,

For design example eth_e2e_e10,

1,May I know where I can check the c code or SV code for 10G mac configuration in design example eth_e2e_e10?

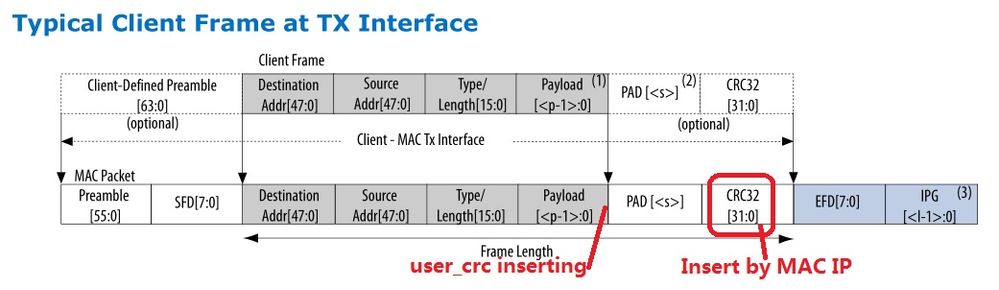

2,As to CRC checksum, I have noticed avalon_st_gen.v has a 4 bytes CRC checksum been inserted in the last of stream to the MAC, I know customer has option either to generate CRC by themselves or leave it to MAC IP for automatic CRC inserting. Can I understand the tx_crc_control[1] was set to 0 to disabling CRC inserting by MAC IP ,therefore user need to generate CRC checksum by themselves? If so ,where can I find this register writing configuration code in what design file? Also If I managed to set tx_crc_control[1] to 1,which means I can remove CRC generation code from avalon_st_gen.v without influcing the function?

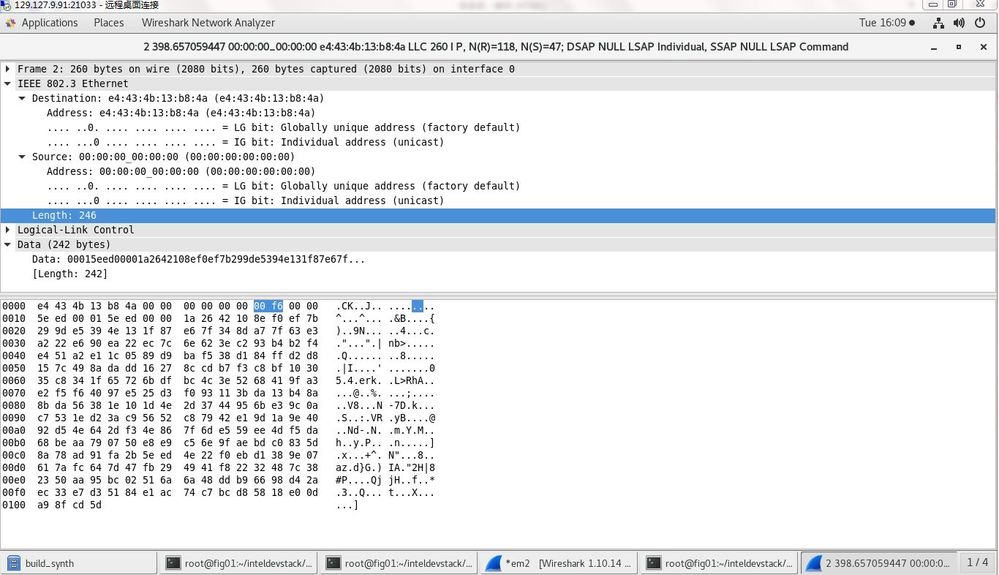

3,I have found the length number I have send through command does not match the length number catching by wireshark, there are 4 byte difference. For example

I sent 1 packet with length 0x108 as below over channel 0

./pac_hssi_e10 -b 0xd8 -d 00 -f 00 -p 0x01 -l 0x108 -s 0:0:0:0:0:0 -m e4:43:4b:13:b8:4a --channel=0 --action=pkt_send

Wireshark got this packet, but only catched 0x104 bytes, 4 bytes missing, can you give some suggestion? Thanks

Jim

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

HI,

I would suggest you go through the Ethernet 10G user guide doc first to learn about the IP feature as you may already find some answer in the doc itself.

- https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug_32b_10g_ethernet_mac.pdf

I am not sure you are using Arria 10 FPGA or Stratix 10 FPGA but you can also check out below design example guideline doc to learn more about the design structure and also register setting control (for instance : tx_crc_control reg address mapping location)

Arria 10 example design :

Stratix 10 example design :

Thanks.

Regards,

dlim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi dlim,

thanks for your feedback. I am using Intel PAC Arria10gx dev kits.

The design example I mentioned is under OPAE installation directory. root/inteldevstack/a10_gx_pac_ias_1_2_pv/hw/samples/eth_e2e_e10/

I have done some PAC test with Quartus 17.1 on centos 7.

my question is about design example provided by Intel.

design eth_e2e_10 is more than 10GE IP and it's example,because it also involved CCIP comunication and other things.

if you are familar with this design example , please give me some suggestion.

Best regard

Jim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jim,

Sorry, I am not aware you are referring to Intel PAC Arria10gx 10G Ethernet example design issue.

I am not familiar with PAC card but I google and find out some info on this example design that perhaps you can checkout.

You can learned more about the 10G Ethernet IP architecture in below link :

As for the example design debug, below is the doc

- https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug-dex-afu-10gbe.pdf

- Just wonder have you try run the example design directly without modification to check if it works first ?

- Does it failed on all 4 10G Ethernet link or just 1 or 2 link ?

- Other generic Ethernet debug suggestion will be like

- test out internal loop back mode

- Then follow by external loopback mode (using QSFP loopback module)

- finally only you proceed to try out on wireshark to slowly isolate where is the issue

Thanks.

Regards,

dlim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

You will need to modify the RTL code as the design example is using Pattern Generator and Pattern Monitor in order to verify the Ethernet packats. In the RTL code, you will observed Avalon_st_gen and Avalon_st_mon.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi JohnT,

Thanks for your feedback and support.

I think your suggestion is a possible way I have interest to follow.

I have check the userguide of low latency 10G MAC and found

CRC checksum automatically inserting to stream in the frame can be enable or disable by the register tx_crc_control,which is in the offset 0x0026 of TX configuration and states register.

Unfortunately ,I have not found any specific SV OR V code to write or read CSR of MAC in the hardware code under the location \..\examples\eth_e2e_e10\hw\

I guess that part is done by CPU side through the CCIP, that is why I have not seen the specific CSR configuration value and check them.

I would like to check these 10GE MAC CSR value in these design example ,so I could know how the MAC being configured and worked, which can be used to explain several questions like

1,where the missing four bytes from wireshark ? if the last 4 crc-check sum, generated by the user code, is being treated as part of payload ,and on top of that, MAC IP still insert another extra crc checksum into the end of stream probably, then the last 4 bytes crc value might not be able to see on wireshrk.

CRC probably being computing twice I guess lie below, once is done by the user design code CRC32_gen, and another CRC check sum is automatically add into the stram and invisible to user .I need csr VALUE to confirm this .

Thanks

Jim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

You will need to refer to "ccip_std_afu.sv" in rtl folder which will shows how is the state machine is being performed by the CCIP to the CSR configuration register,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi JohnT,

Thanks for your feedback and support.

I have checked ccip_std_afu.sv ,and found that is a mapping module from CCIP MmioDin to Ethernet CSR.

But that is just a mapping module, which means the control source and source data is in the upper stream module, I think source is from c code in CPU side.

ccip_std_afu.sv works as a highspeed way to provide a road only, but data source, it can connect different modules but cannot know what data being delivered.

So with that ccip_std_afu.sv,still cann’t fig out what specific value being write to CSR. Thanks

Jim

always @(posedge clk or posedge pck_cp2af_softReset_T1)

begin

if (pck_cp2af_softReset_T1)

begin

afu_init <= 'b0;

ctrl_addr <= 'b0;

wr_data <= 'b0;

afu_scratch <= 'b0;

end

else

begin

if (cp2csr_MmioWrEn)

case (csr_addr_8B[3:0])

AFU_INIT [6:3]: afu_init <= cp2csr_MmioDin;

ETH_CTRL_ADDR[6:3]: ctrl_addr <= cp2csr_MmioDin[31:0];

ETH_WR_DATA [6:3]: wr_data <= cp2csr_MmioDin[31:0];

AFU_SCRATCH [6:3]: afu_scratch <= cp2csr_MmioDin;

default: ;

endcase

end

end

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Please refer to https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/manual/mnl-ias-ccip.pdf which will explain how the interface with CCIP and you can use the "dma_afu/sw" as a reference on how to send the data or csr to the CCIP.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page