- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I get a similar error on the same data pin on a 2nd EMIF instance. It appears the pinout follows all the requirements but still getting the errors below:

Error(14566): The Fitter cannot place 2 periphery component(s) due to conflicts with existing constraints (2 DQ_GRP(s)). Fix the errors described in the submessages, and then rerun the Fitter. The Intel FPGA Knowledge Database may also contain articles with information on how to resolve this periphery placement failure. Review the errors and then visit the Knowledge Database at https://www.intel.com/content/www/us/en/support/programmable/kdb-filter.html and search for this specific error message number.

Error(175020): The Fitter cannot place logic DQ_GRP that is part of External Memory Interfaces Intel Agilex FPGA IP emif_altera_emif_fm_262_qridiwq in region (226, 0) to (227, 0), to which it is constrained, because there are no valid locations in the region for logic of this type.

Info(14596): Information about the failing component(s):

Info(175028): The DQ_GRP name(s): platform0|emif_fm_1|emif|arch|arch_inst|io_tiles_wrap_inst|io_tiles_inst|tile_gen[0].lane_gen[0].lane_inst|lane_inst_DQ_GRP_1

Error(16234): No legal location could be found out of 1 considered location(s). Reasons why each location could not be used are summarized below:

Error(175005): Could not find a location with: DQ_X9 (1 location affected)

Info(175029): DQ_GRP containing LN32

Info(175015): The I/O pad mem_dq[1][7] is constrained to the location PIN_MC29 due to: User Location Constraints (PIN_MC29)

Info(14709): The constrained I/O pad is contained within a pin, which is contained within this DQ_GRP

Error(175020): The Fitter cannot place logic DQ_GRP that is part of External Memory Interfaces Intel Agilex FPGA IP emif_altera_emif_fm_262_qridiwq in region (171, 0) to (172, 0), to which it is constrained, because there are no valid locations in the region for logic of this type.

Info(14596): Information about the failing component(s):

Info(175028): The DQ_GRP name(s): platform0|emif_fm_0|emif|arch|arch_inst|io_tiles_wrap_inst|io_tiles_inst|tile_gen[0].lane_gen[0].lane_inst|lane_inst_DQ_GRP_1

Error(16234): No legal location could be found out of 2 considered location(s). Reasons why each location could not be used are summarized below:

Error(175005): Could not find a location with: DQ_X9 (2 locations affected)

Info(175029): DQ_GRP containing MC39

Info(175029): DQ_GRP containing MC39

Info(175015): The I/O pad mem_dq[0][7] is constrained to the location PIN_MC39 due to: User Location Constraints (PIN_MC39)

Info(14709): The constrained I/O pad is contained within a pin, which is contained within this DQ_GRP

Error(175020): The Fitter cannot place logic DQ_GRP that is part of External Memory Interfaces Intel Agilex FPGA IP emif_altera_emif_fm_262_qridiwq in region (226, 0) to (227, 0), to which it is constrained, because there are no valid locations in the region for logic of this type.

Info(14596): Information about the failing component(s):

Info(175028): The DQ_GRP name(s): platform0|emif_fm_1|emif|arch|arch_inst|io_tiles_wrap_inst|io_tiles_inst|tile_gen[0].lane_gen[0].lane_inst|lane_inst_DQ_GRP_1

Error(16234): No legal location could be found out of 1 considered location(s). Reasons why each location could not be used are summarized below:

Error(175005): Could not find a location with: DQ_X9 (1 location affected)

Info(175029): DQ_GRP containing LN32

Info(175015): The I/O pad mem_dq[1][7] is constrained to the location PIN_MC29 due to: User Location Constraints (PIN_MC29)

Info(14709): The constrained I/O pad is contained within a pin, which is contained within this DQ_GRP

Info(14596): Information about the failing component(s):

Info(175028): The DQ_GRP name(s): platform0|emif_fm_1|emif|arch|arch_inst|io_tiles_wrap_inst|io_tiles_inst|tile_gen[0].lane_gen[0].lane_inst|lane_inst_DQ_GRP_1

Error(16234): No legal location could be found out of 1 considered location(s). Reasons why each location could not be used are summarized below:

Error(175005): Could not find a location with: DQ_X9 (1 location affected)

Info(175029): DQ_GRP containing LN32

Info(175015): The I/O pad mem_dq[1][7] is constrained to the location PIN_MC29 due to: User Location Constraints (PIN_MC29)

Info(14709): The constrained I/O pad is contained within a pin, which is contained within this DQ_GRP

Error(175005): Could not find a location with: DQ_X9 (1 location affected)

Info(175029): DQ_GRP containing LN32

Info(175015): The I/O pad mem_dq[1][7] is constrained to the location PIN_MC29 due to: User Location Constraints (PIN_MC29)

Info(14709): The constrained I/O pad is contained within a pin, which is contained within this DQ_GRP

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Brian,

Can you share the example design that can replicate the issue?

I can check the error at my end.

Regards,

Adzim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

example design with qsf updated with pinout is attached below.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Brian,

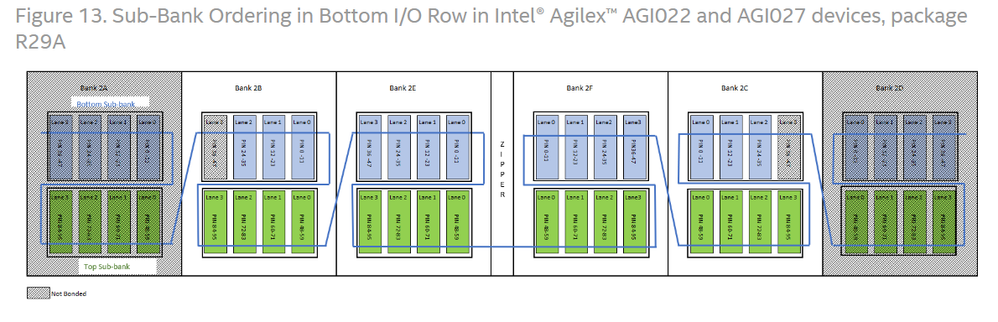

I have checked the design at my side and I can see that the data pins placement are placed in IO Bank 2D while the Address and Command pins are placed in IO Bank 2C.

For your information, the IO Bank 2C and IO Bank 2D are not bonded in Agilex AGI027 devices.

That is why the pin placement cannot be made in those IO Bank.

You can use IO Bank 2F for the data pins and IO Bank 2C for Address and Command pins.

Regards,

Adzim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Adzim,

According to the "Intel Agilex FPGA EMIF IP – Product Architecture 683216 | 2022.11.03", and the agib027.xlsx for the R29A show the AGI027 in R29A package has 2A and 2D not bonded. 2B, 2E, 2F, and 2C are bonded. Is that not accurate? And according to my tripled verification of the pins used, we are using 2F for data, and 2C for address and command. Can you give an example pin that is in bank 2D?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Brian,

That is accurate. What I mean is the connection between the IO Bank 2C and IO Bank 2D is not bonded.

I will attach the example design in .qar file.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Adzim,

I see the updated qsf from your *.qar file, but I don't understand what is wrong with the pinout we used. The banks and IO lanes used are the same just different DQ/DQS groups are in different locations. What rule is being violated?

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Adzim,

In looking at the qsf from your *.qar file, there are a number of nibbles that aren't contained in a nibble, they cross the nibble boundary (they stay in the byte).

Example:

set_location_assignment PIN_LH42 -to emif_mem_mem_dq[71]

set_location_assignment PIN_LL43 -to emif_mem_mem_dq[70]

set_location_assignment PIN_LL39 -to emif_mem_mem_dq[68]

set_location_assignment PIN_KW43 -to emif_mem_mem_dq[69]

set_location_assignment PIN_KW41 -to emif_mem_mem_dqs_n[17]

set_location_assignment PIN_LB40 -to emif_mem_mem_dqs[17]

set_location_assignment PIN_MA34 -to emif_mem_mem_dqs_n[8]

set_location_assignment PIN_LW33 -to emif_mem_mem_dqs[8]

set_location_assignment PIN_KW39 -to emif_mem_mem_dq[65]

set_location_assignment PIN_LB38 -to emif_mem_mem_dq[64]

set_location_assignment PIN_LB42 -to emif_mem_mem_dq[66]

set_location_assignment PIN_LH38 -to emif_mem_mem_dq[67]

LL39 is in DQ44, while LH42, LL43, and KW43 are in DQ45.

How did you generate this pinout for the EMIF? And what is wrong with the one we generated? If I don't know what is wrong I can't fix it on other EMIF interfaces.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Brian,

When you are doing pin assignment, please make sure the port name and signal name is exist in the design. The top level design will contain all required signal.

For data pin by x4 group, the DQS0 must be paired with DQS1 in an IO lane. In general, DQS(x) and DQS(x+1) must be paired in the same IO lane.

Regards,

Adzim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

DQS numbering helped one of the 2 banks. 2nd one still failed with the same error. So I just mirrored the one passing ones pinout to get the 2nd emif to get past it and that worked.

No accepted solution on this as they never could tell me what the problem was. Just giving a working pinout doesn't help, showing what is wrong is helpful because then others can avoid it.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Brian,

Thank you for your feedback in this thread.

Which area that I can further assist you in this issue?

Regards,

Adzim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

As we do not receive any response from you on the previous reply that we have provided, I now transition this thread to community support. Please login to ‘https://supporttickets.intel.com’, view details of the desire request, and post a feed/response within the next 15 days to allow me to continue to support you. After 15 days, this thread will be transitioned to community support. The community users will be able to help you on your follow-up questions.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page