- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

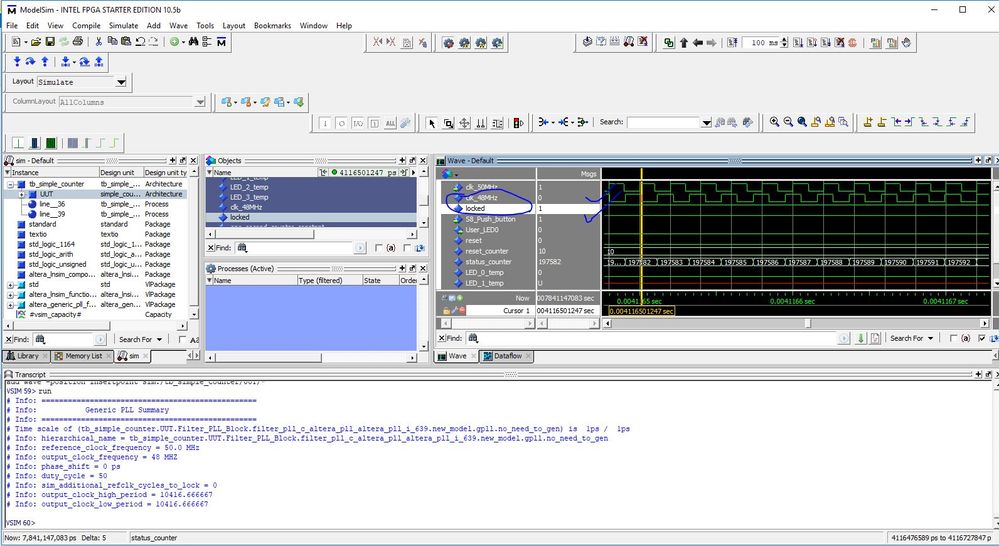

I'm trying to implement the Altera PLL from the IP catalog and no matter what I do- this simple cure is not working! (outclk_0 is constantly red signal in ModelSim). I'm working with Quartus Prime Lite Edition 17.1, ModelSim 10.5b and 5CEFA7F31I7 Cyclone V FPGA (EVM).

My ref clock is 50MHz and the desired and the actual is 48MHz. The other parameters are default (Direct, Integer-N PLL, Phase shift 0ps, D.C=50%, with locked output signal and input reset signal (active high but I even tried to toggle is in 1Hz).

What could possibly be the cause for the standard PLL cure???

Help…

Idan

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Idan,

- Have you applied reset?

Try applying reset and given appropriate inputs to get the expected output.

Regards

Anand

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I did… as I mentioned, I even toggle the reset at 1Hz. The ref clk is always present at the input signal.

What else can I do to operate the PLL cure?

Help…

Idan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Idan,

Are you using just PLL IP stand-alone or initiating PLL IP on top-level HDL for simulation? Check the connectivity of the ports or pins.

Try after deleting the work folder from the simulation directory.

Attached some images.

Regards

Anand

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Here are some snap shots from my code and simulation (and I'm attaching the project itself).

Help...

Idan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

And the complete code that is not working (PLL output is all red (U)).

What can I do to make it work?

Can you try to run the code in your Quartus and ModelSim versions?

Thanks,

Idan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Idan,

Your design looks good, You have to recheck the simulation steps. Please read msim_setup.tcl(Simple_counter_PLLC\Filter_PLL_C_sim\mentor) file which will help in simulation step if you have top level file.

I have attached the modelsim transcript and image. save below code as mentor.do and run

set QSYS_SIMDIR C:/<Directory>/Simple_counter_PLLC/Filter_PLL_C_sim

source $QSYS_SIMDIR/mentor/msim_setup.tcl

dev_com

set TOP_LEVEL_NAME tb_Simple_counter

elabRegards

Anand

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page