Hi all!

For writing/reading coefficients I made a wrapper to compute the proper reset before accessing the Avalon slave.

Writing seems to work fine but reading has issues

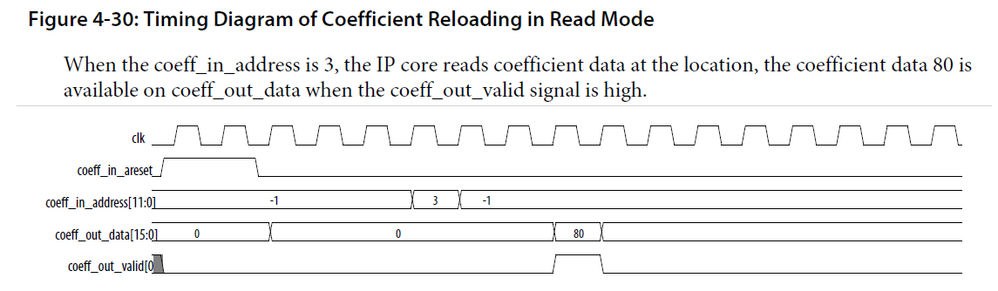

Considering the FIR II IP Core User Guide and the read waveform:

As you can see they forgot to add the read signal (read enable) to the waveform.

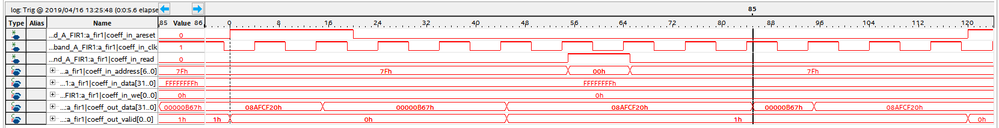

If I capture the signals with the Signal Tap Logic Analyzer (Quartus 17.1), the behavior is completely different!:

As you can see in the waveform above the reset is right and the address and read signal is set after the same amount of clock cycles. 3 clock cycles later the proper data shows up on the read interface but the valid signal comes much earlier and therefore the behavior is wrong and does not correspond to the user guide.

Behavior in Quartus 15.1 is wrong as well as the valid signal is never set there!

I will provide later a capture with the Signal Tap Logic Analyzer.

Kind regards,

Erich

链接已复制

Hi Chee Pin!

Yes I have a concern regarding that topic!

In real live there is always a valid address assigned to the input.

If the filter has 256 coefficients there is then no invalid address possible because input width is exactly 8 bit!

So in a real implementation the valid would be always high!

By the way, you should not have negative addresses ;-)

Best regards,

Erich