- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi folks,

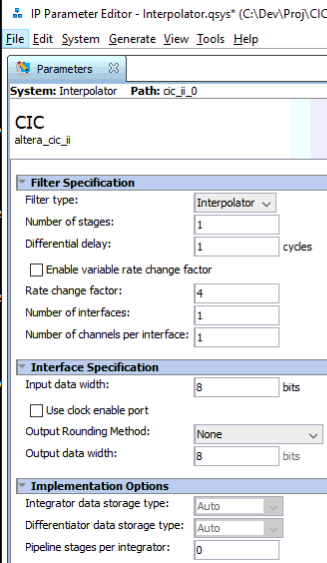

I'm trying to simulate a CIC interpolator. I noticed that when the number of stages is a power of 2 (1,2,4 or 8, since the maximum is 12), I only get zeroes as the output. Any other value for the number of stages is fine. Here are screenshots of my IP configuration:

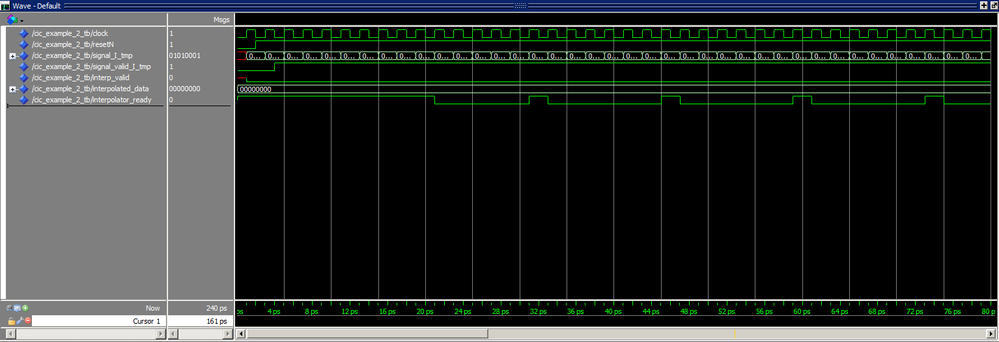

And here is one of my simulation. The signal_I_tmp is what I feed to the interpolator. It is an 8-bit signed which increments by one at each clock. Then, the interp_valid is the out_valid of the IP and it stays low.

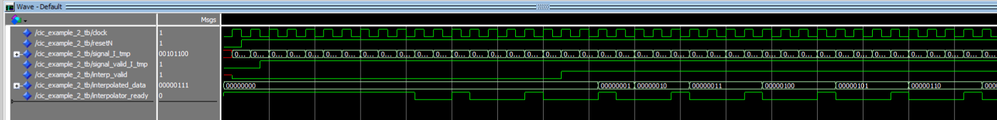

If I only change the number of stages to 3 and choose "rounding up" instead of "none" as the output rounding method, it works:

So would any of you know why the powers of 2 don't work?

Thanks for your time,

Carl

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi cpchan,

Attached is a simple test design - the one I used to capture the above screenshots. To reproduce the issue:

- Unzip project

- Open ModelSim

- open CIC_Example_2_tb.mpf

- In the TCL console: source Interpolator/simulation/mentor/simulation.tcl

- In the TCL console: run 120 ps

Thanks for your time looking into this issue,

Carl

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

thanks for sharing the files. Please allow me some time to look into it. I will update you on the progress by mid of next week. Please ping me if you do not hear back from me. Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Sorry for the delay. I have been performing a number of tests on my side. I observe that with default configuration of the CIC Interpolator (stage = 12, rate change = 8, rounding = none), there is no issue with the simulation output using IP generated example design in Q18.1Pro. As I cross check with your Interpolator.qsys, I notice that the number of stage is set to 1 in your configuration. As I tested setting stage = 1 and run the IP generate example design, I can observe output data and valid = 0. Based on these observation, we can narrow down to the parameter "Number of stages" set in your failing case. Would you mind to increase this parameter to 12 to see if it helps on your side?

Please let me know if there is any concern. Thank you.

Best regards,

Chee Pin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Chee,

Thanks for looking into this. It does work when I use the default value of 12 stages. My question is specifically about the powers of two, as I would like to use such values in my design.

Regards,

Carl

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

thanks for your update. For your information, I am able to replicate the observation when using number of stages = 4 and 8, the output stuck at 0. There is no issue when I use 3,5 and 7. I have filed a case to Engineering on this to seek for further clarification. I will update you on the progress by mid of next week or as soon as there is any valid response. Please ping me if you do not hear back from me. Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

For your information, I am still pending for valid response from Engineering on this. I will continue to follow up and update you on the progress early next week or as soon as there is any valid response. Sorry for keeping you waiting.

As a workaround, just wonder if you are able to use non power of 2 to avoid gating your progress?

Also, a correction to my previous post, in my replication, there is no issue when I use 3, 5 and 7. The 8 is a typo. Sorry for the inconvenience.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Chee,

Thanks for the update. In our design we specifically want one stage so we will wait for the response from the engineering team.

Carl

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Carl,

Thanks for the update. I have dropped Engineering separate email to facilitate response. Please ping me if you do not hear back from me next week. Sorry for the delay.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Carl,

Sorry for keeping you waiting. I still have not receive valid response from Engineering. I will continue to ping them for response. Please ping me if you do not hear back from me by end of next week. Sorry for the delay.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Chee,

It's been three weeks now since you reproduced the issue. Are the engineers working on it at the moment? What is the estimated time of completion?

Carl

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Chee,

I'm not aware of my local FAE. Did you escalate the issue?

Carl

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Carl,

Thanks for your update. For your information, I have escalated and seek assistance from Factory on this. However, I have yet to receive any valid response from Factory. I will continue to follow up closely and drive for valid response.

Sorry for the inconvenience.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Carl,

I would like to apologize for the delay as I have yet to receive valid response from Factory. I am so sorry for the inconvenience and I will continue to escalate this issue for valid response.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Carl,

For your information, I have yet to receive any valid finding from Factory on this. I believe Factory is currently tied up. I understand that this has been dragging for quite some time. To avoid gating your progress further, just wonder if you would be able to look into using other value which is not power of 2? Sorry for all the inconvenience.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page