- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi everyone,

I came across two problems when reading IP generation part of "Intel® Quartus® Prime Pro Edition User Guide Platform Designer 20.1 version" and I would like to kindly ask for assisstance.

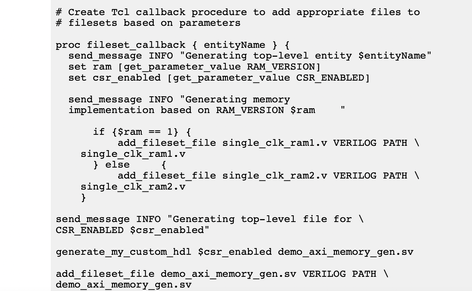

Question one is at page 134, the example of generating the component using script "generate_my_custom_hdl $... .().sv". May I ask what is "generate_my_custom_hdl"? Without this, are there other commands in the generate_callback proc to generate the .sv IP?

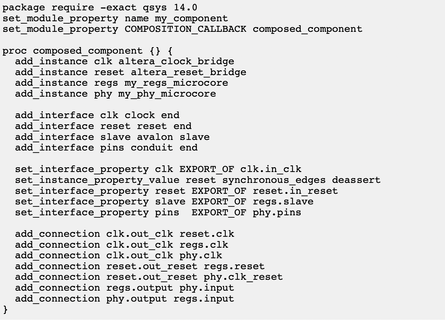

Question 2 is at page 136, example of designing composed components.

From this example, I am not sure what file_set_file I need to add if I want to generate this IP. This IP have 4 instances, with two of them being customized one. Sometimes a customised IP may have multiple synthesis file in their QUARTUS_SYNTH file sets. Do I only need to add the custom IP file or the whole file sets behind them?

For instance, if "my_regs_microcore_hw.tcl" has my_regs_microcore.v, verilog1.v, verilog2.v...verilogn.v; do I need to only add the my_regs_microcore.v for composed component or all these files?

Thank you in advance!

Mingqiang

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @cosx

Sorry for the late reply. Do you need further help regarding to this case? Do you able to solve the issue?

*A composed component is a subsystem containing instances of other components.

*Unlike an HDL-based component, a composed component's HDL is created by generating HDL for the components in the subsystem.

I don't think you need to defined the synthesized fileset of all files in the composed component as this was defined prior in each _hw.tcl file of each sub IP.

Best Regards,

Richard Tan

p/s: If any answer from the community or Intel support are helpful, please feel free to give Kudos.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I think generate_my_custom_hdl is just an example function name showing how you would then create the custom HDL yourself (with your own function) and then add that created file (the .sv file) to the fileset.

For the composed component, you would need all the files that make up the individual instances (defined in the fileset in each _hw.tcl file) within the composed component. Maybe I'm not understanding your thinking about not including all the files. If you don't include all the files, how would the individual instances work?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you so much for your reply!

My second point is more about composed IP generation. Currently the document did not give any example code of the whole generation.

For instance, if I have a composed IP that contains 3 sub customised IPs, how can I generate this composed IP?

Do I just need to add synthesized fileset of all files and then the composed IP .v is generated, or need extra commands?

Could you please give me a bit more details of this if possible?

Thank you again!

Mingqiang

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @cosx

Sorry for the late reply. Do you need further help regarding to this case? Do you able to solve the issue?

*A composed component is a subsystem containing instances of other components.

*Unlike an HDL-based component, a composed component's HDL is created by generating HDL for the components in the subsystem.

I don't think you need to defined the synthesized fileset of all files in the composed component as this was defined prior in each _hw.tcl file of each sub IP.

Best Regards,

Richard Tan

p/s: If any answer from the community or Intel support are helpful, please feel free to give Kudos.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page