- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

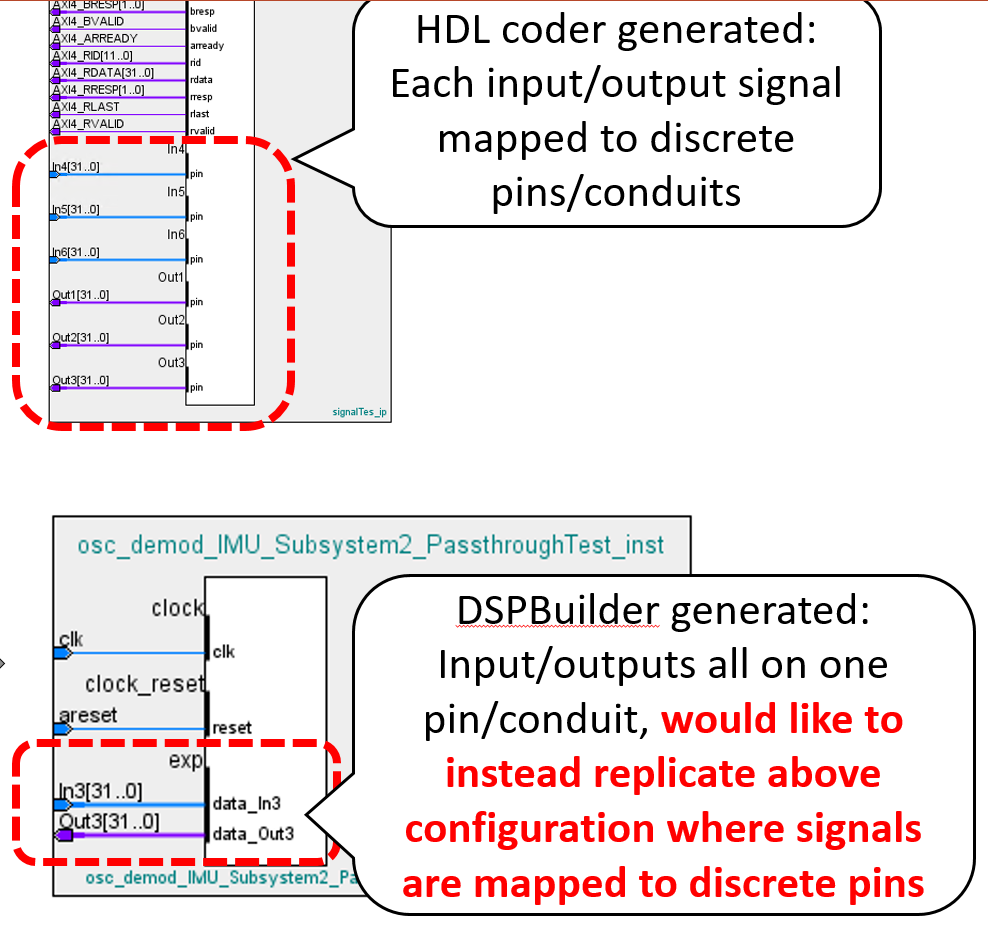

In my system, I use MATLAB HDL coder to generate an IP core facilitating host to target communication with an AXI bus, and a set of external data signals each mapped to their own distinct individual connection points i.e. "conduits".

I also use DSP Builder to generate an IP core specializing in NCO/Mixer/Filter components, also containing ports for external data signals.

I import both of these IP cores as custom components in an existing Qsys/platform designer project for my board (DE10-Nano). I have been using page 66 of this DSPBA manual as a reference guide for importing DSPBuilder-generated custom components into Qsys/Platform designer.

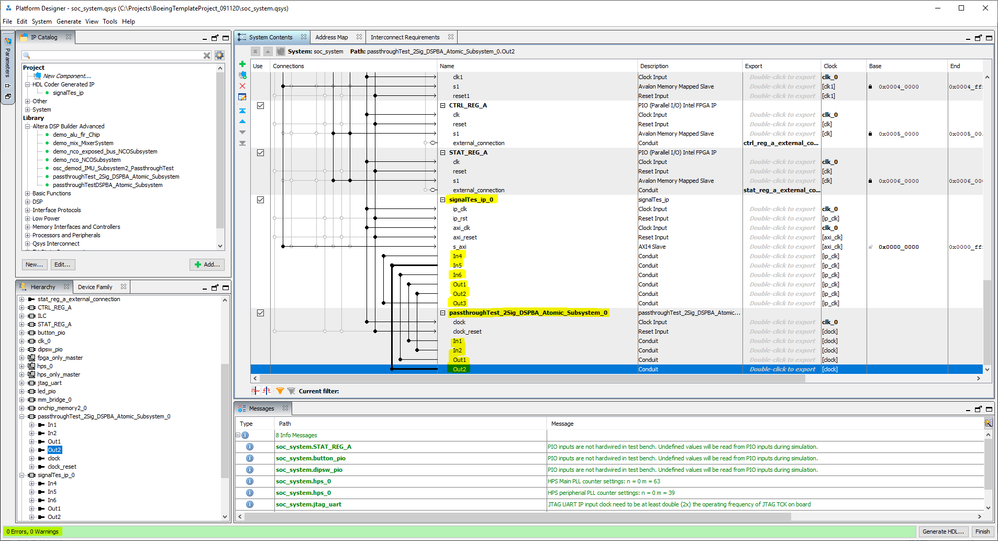

I intend to connect several data signals between the HDL coder custom component and the DSP Builder custom component in Qsys.

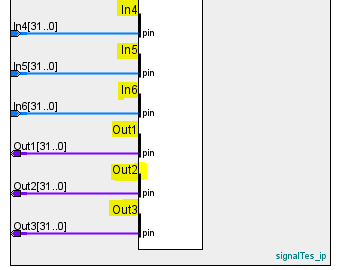

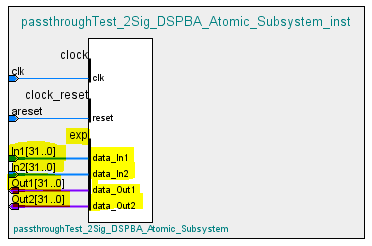

The problem that I have been running into is that the HDL coder and DSP builder-generated custom components seem to follow different conventions for mapping their data signals to connection points in Qsys i.e. "conduits". An example of the Qsys implementation of an HDL coder custom component and a DSP Builder custom component are shown below, from top to bottom.

I would like to customize the DSPBuilder-generated custom component (bottom) to have the same data-signal-to-conduit mapping convention in Qsys as the HDL coder generated custom component in Qsys (top). In other words, I would like each of the data signals on the DSPBuilder-generated custom component (data_In3, data_Out3) each mapped to their own distinct conduits, to facilitate directly connecting them to distinct data signal conduits on the HDL-coder generated custom component (In4, In5, ... Out2, Out3).

An example of this kind of connection between Qsys components shown in the above screenshot would be connecting Out1 on HDLCoder component --> In3 on DSPBuilder component, and connecting Out3 on DSPBuilder component to In5 on HDLCoder component.

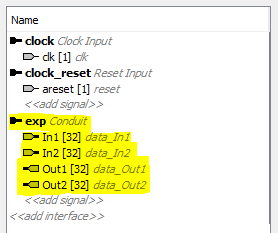

Currently, DSP Builder generated custom components have all of their data signals mapped to one single conduit labeled "exp", making it difficult to connect data signals between this DSP Builder generated custom component and an HDL coder generated custom component.

How would I go about editing the DSP Builder generated custom component to ensure that each of its external data signals are mapped to distinct individual conduits in Qsys, instead of being all lumped into a single conduit "exp"? Is there an option to configure this data-singal-to-conduit mapping in the MATLAB Simulink DSPBA Blockset, or would I have to manually edit the generated _hw.tcl file used to import the custom component into Qsys?

Best,

- Gheorghe S

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear all,

I found a workaround for my problem on my own, thanks to your tips.

The workaround procedure I developed for configuring DSP Builder-generated custom components to ensure their data signal ports are compatible with connecting to data signal ports on HDL Coder-generated custom components in Platform Designer/Qsys is as follows:

1. Generate _hw.tcl representing contents of DSPBuilder IP core using MATLAB play button.

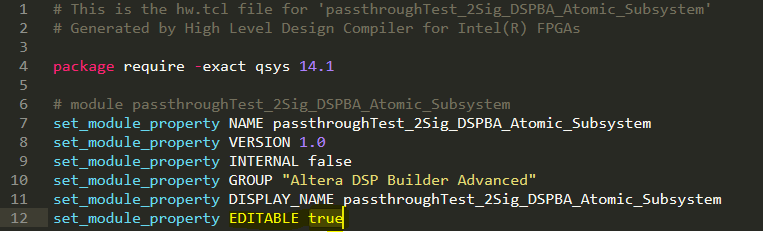

2. Edit _hw.tcl using any text editor, set EDITABLE property to "true" near top of file

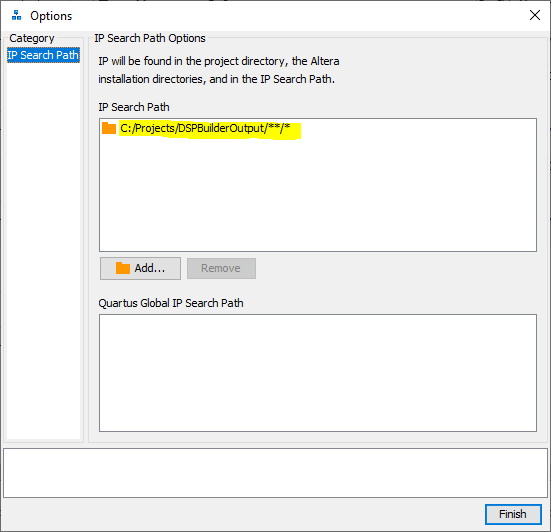

3. Import _hw.tcl into Platform Designer by adding folder containing _hw.tcl and .vhd files to IP catalog search path via Platform Designer top toolbar Tools >> Options.

4. Select DSP Builder IP core (aka custom component), select Edit...

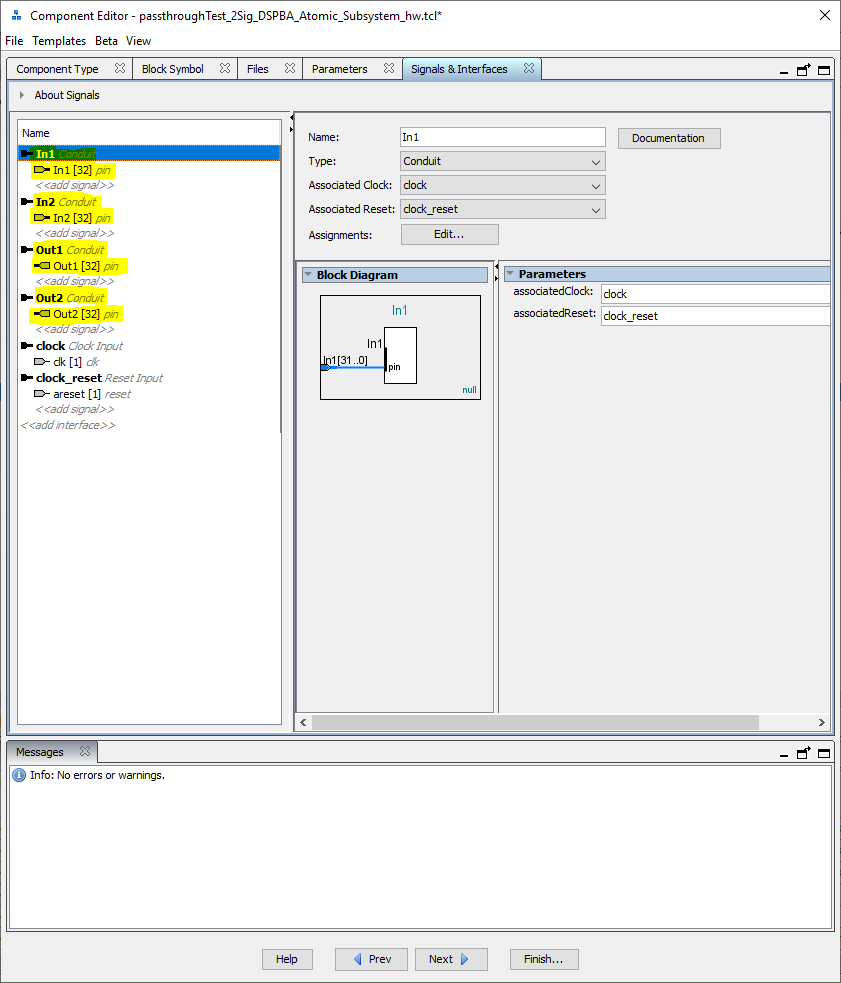

5. Go to Signals & Interfaces tab...

- Add one new conduit for each data signal.

- Drag one data signal to each conduit.

- Set clocks and resets for each conduit.

- rename each conduit from [conduit_end1, conduit_end2, ...] to [In1, In2, ... Out1, Out2...] (corresponding to data signal name).

- For each signal, recast "signal type" from [data_In1, data_In2...] all to just "pin".

- Delete original "exp" conduit.

6. Finish, save + overwrite edits, now "port edits" appear at the end of _hw.tcl file.

7. Copy "port edits" at end of _hw.tcl file.

8. Regenerate _hw.tcl file for DSPBuilder IP core using MATLAB play button.

9. Edit _hw.tcl using text editor, add "port edits" to end of _hw.tcl file, replacing "exp" conduit interface declaration.

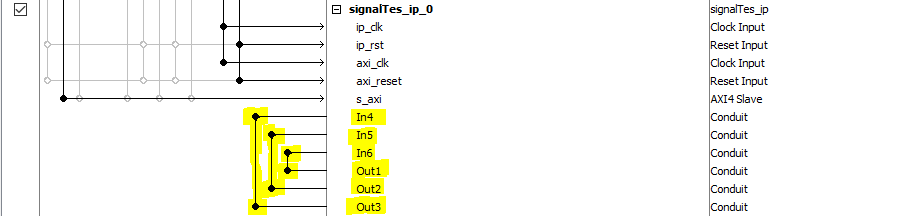

10. Refresh Platform Designer using F5, add IP core to project. Now data signal conduits are properly configured for connecting to data signal conduits on MATLAB HDL Coder generated blocks, shown below.

Thank you to @sstrell for pointing out the easy/repeatable/bug-free way to edit conduit/data signal assignments from the Qsys component editor.

I borrowed this method to generate the _hw.tcl code necessary to define my custom port configuration.

Unfortunately in doing so, the rest of the _hw.tcl file was "wiped clean", but it is easy to regenerate in MATLAB.

I took the port configuration code generated from the component editor, and added it to my re-generated _hw.tcl file, and after refreshing Qsys, the ports on my DSPBA custom component are configured correctly.

Although slightly roundabout, this consistent UI-based procedure seems to work every time. Also, the port configuration _hw.tcl code generated from the component editor is re-usable as long as the DSPBA in/out data signals remain unchanged.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm not familiar with DSP Builder much, but as far as editing an existing custom component, just right-click the custom component in the IP Catalog and select Edit to open the Component Editor. Then go to the Signals & Interfaces tab. There you can add conduit interfaces and drag and drop the signals around to move them and organize them however you want. Since these are conduit signals and not part of any standard interfaces, you can organize them however you wish. Click Finish to create an updated _hw.tcl file for the component.

I don't know if that helps.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Sstrell,

Thank you for the quick reply, this seems like promising advice.

Unfortunately, after importing a DSPBuilder-generated custom component by including its generated files in the IP Catalog search path, I am unable to select the edit option. Do you know if DSP Builder-generated custom components are write-protected somehow?

If so, how can I disable this write protection, or import these DSP Builder custom components in a way that allows me to edit them after importing?

Best,

- Gheorghe

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hmm. Maybe you can manually edit the _hw.tcl file which I assume is generated by DSP Builder (which again I could be wrong about). It's trickier to reorganize signals this way, but if you can edit the _hw.tcl file in a text editor, you should be able to figure it out using the Platform Designer user guide, which describes the commands in _hw.tcl files.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

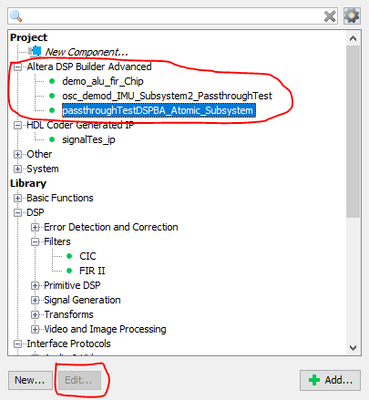

Here is a screenshot of what occurs when I try to edit these DSP Builder generated custom components: it seems like the "Edit" button is grayed out.

Thank you for the tip on editing the _hw.tcl file, I will give that a shot.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Gheorghe,

By default, all Intel FPGA IP is locked where Intel not want user to modify the hw.tcl files.

The reason is those exp buses are design as a conduit. simply modify the hw.tcl to other type of signal will not work.

There are two ways you can work on this.

1) to make it to AVST, or any other interface. You will need to recreate a custom component to wrap around it. and the interface you need to redesign as well as the it's original are just conduit.

it's easy to implement... Just put your data on the data bits, assert 'valid' when the data from the A/D is there, and wait until 'ready' is asserted. When it is, de-assert 'valid' and prepare the next data word.

You can refer to the spec for it here: https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/manual/mnl_avalon_spec.pdf page 40

Also, you need to Add Component Instances in your hw.tcl files in order to call out the demo_nco_subsystem IP.

you can refer to https://www.intel.cn/content/www/cn/zh/programmable/documentation/zcn1513987282935.html?

Look for session 2.9. Add Component Instances to a Static or Generated Component

You can look for the demo_nco_subsystem hw.tcl files, by right click in it in the IP catalog -> details -> location

2) second way would be much simpler, just design create custom component for convertor from BUS to avalon ST. You are going to do it same way in number 1 anyway.

You can refer to https://www.youtube.com/watch?v=v6rhbVABlo8

For visibility of the signal, you can just click on Tools -> hierachy.

Thanks,

Best regards,

Kenny

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear @KennyTan_Altera,

Thank you for the suggestions.

1. My goal is to output my DSP Builder data signals on "vanilla" conduits that do not conform to Avalon ST format (i.e. do not have valid/channel signals), to simplify high-level development for my team.

I believe mapping data signals to "vanilla" conduits is possible because we used MATLAB HDL coder to generate and import a custom component in Platform Designer with its data signals mapped to non-AvalonST conduits, and we verified that they work with a passthrough/self-connect test, as shown in the first screenshot below. These "vanilla" non-AvalonST conduits are shown in detail in the second screenshot below.

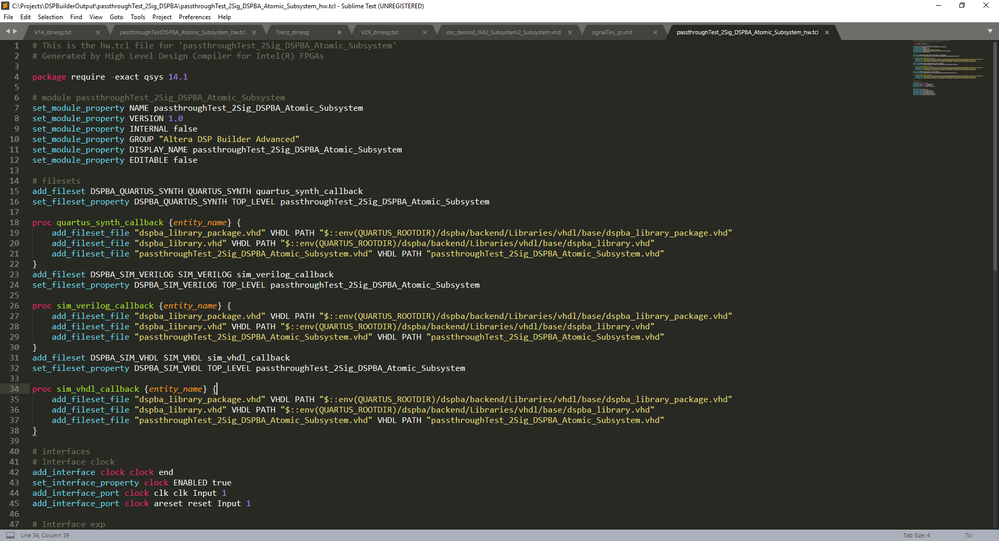

2. After reviewing the DSPBuilder-generated _hw.tcl file, I was able to find the line of code that was preventing me from editing the DSPBuilder-generated custom component in Platform Designer, shown below.

After setting this "EDITABLE" module property to "true" in the DSPBuilder-generated _hw.tcl file, I imported this DSPBuilder-generated IP core as a custom component in Platform Designer by adding the the DSPBuilder-output folder containing the generated _hw.tcl file and its .vhd source files to the Platform Designer search path, as shown below.

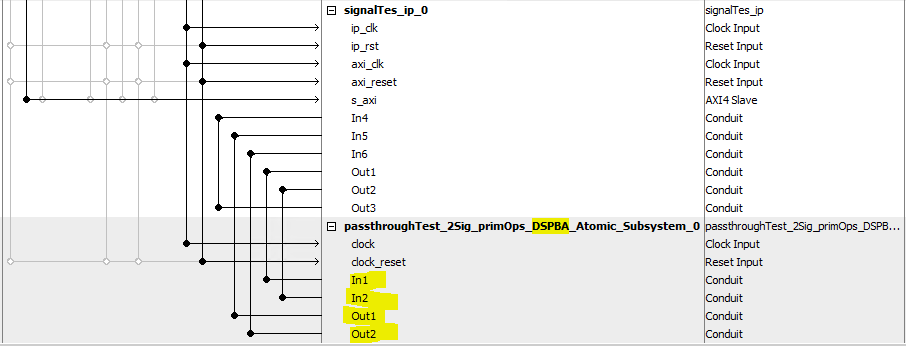

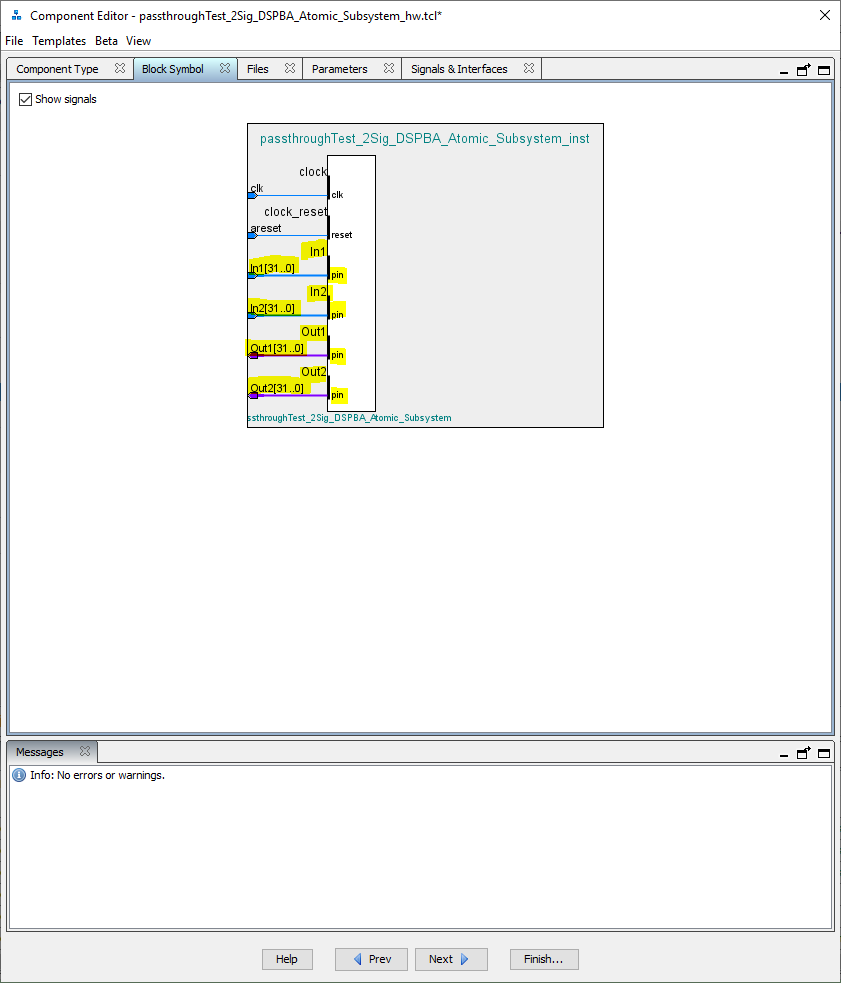

I tried editing this DSPBuilder-generated custom component, and was able to edit the conduit signals by dragging and dropping them into new conduit interface connection points, as Intel Forum user @sstrell suggested earlier in this thread, shown in the below screenshots.

Before editing:

After editing:

With these edits, I can add the custom component into my Platform Designer project, and connect it to my HDL coder-generated custom component with no errors or warnings, as shown below.

However this project fails to compile, because it seems like the .vhd synthesis files for the DSPBuilder-generated custom component are not being imported correctly.

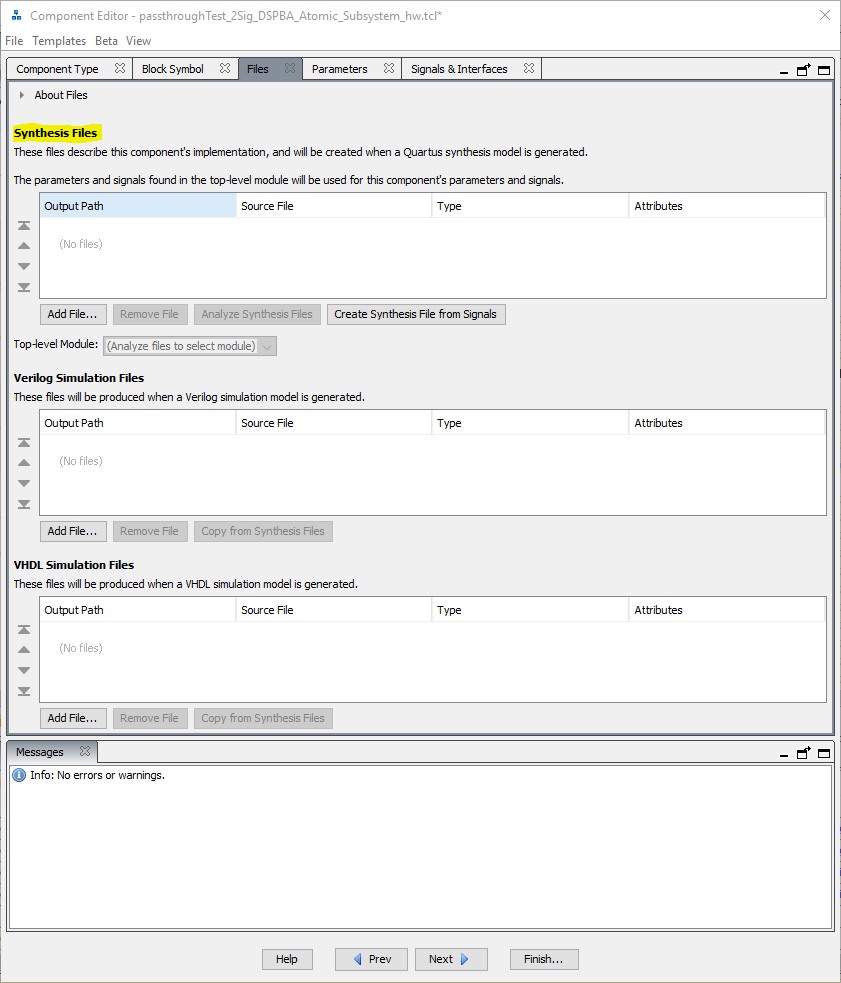

Just after importing the DSPBuilder-generated custom component by including its output files folder containing _hw.tcl and .vhd files, and before making any port edits, there are no synthesis files displayed in the component editor, shown below, even though they are referenced in the _hw.tcl file, also shown below.

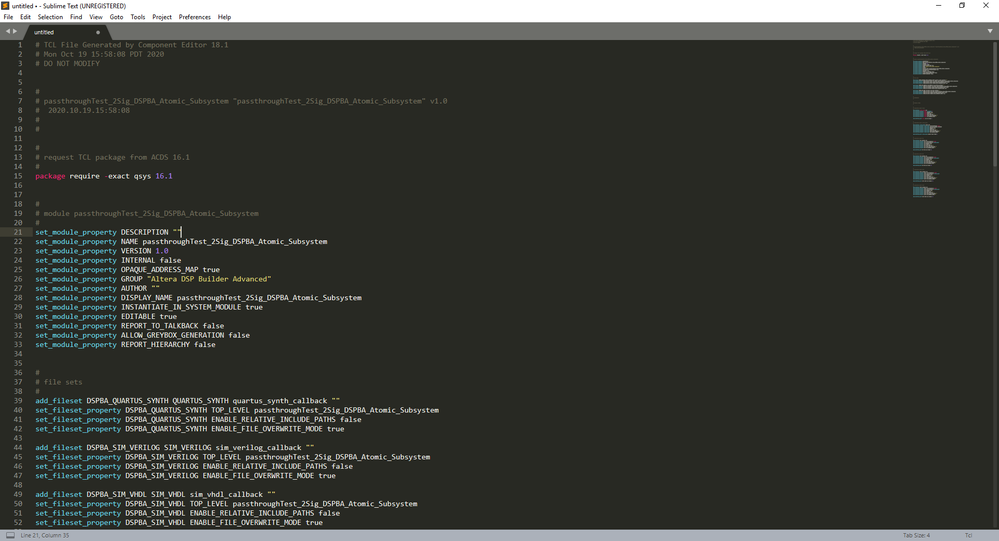

After applying my port edits and overwriting this DSPBuilder-generated custom component, it seems like the .vhd synthesis file references originally shown in the _hw.tcl are wiped clean, where the below screenshot shows the new _hw.tcl file for the DSPBuilder-generated custom component after applying and saving my port edits.

How can I ensure that the .vhd synthesis files originally referenced in the DSPBuilder-generated _hw.tcl file are still automatically referenced after importing into Platform Designer?

Do you see anything wrong with the way that I am importing this DSPBuilder-generated _hw.tcl file as a custom component in Platform Designer?

If these files will not get added automatically, how can I manually add them?

It seems like I would also have to add .vhd file references for "dspba_library_package.vhd" and "dspba_library.vhd", is this true?

I would prefer to find a solution where things are done "automatically" as much as possible, to simplify things and ensure seamless high level development for the rest of my team, to whom I will hand-off this workflow.

Best,

- Gheorghe Schreiber

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Can you check your email on this? We can have a meeting to discuss more.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear all,

I found a workaround for my problem on my own, thanks to your tips.

The workaround procedure I developed for configuring DSP Builder-generated custom components to ensure their data signal ports are compatible with connecting to data signal ports on HDL Coder-generated custom components in Platform Designer/Qsys is as follows:

1. Generate _hw.tcl representing contents of DSPBuilder IP core using MATLAB play button.

2. Edit _hw.tcl using any text editor, set EDITABLE property to "true" near top of file

3. Import _hw.tcl into Platform Designer by adding folder containing _hw.tcl and .vhd files to IP catalog search path via Platform Designer top toolbar Tools >> Options.

4. Select DSP Builder IP core (aka custom component), select Edit...

5. Go to Signals & Interfaces tab...

- Add one new conduit for each data signal.

- Drag one data signal to each conduit.

- Set clocks and resets for each conduit.

- rename each conduit from [conduit_end1, conduit_end2, ...] to [In1, In2, ... Out1, Out2...] (corresponding to data signal name).

- For each signal, recast "signal type" from [data_In1, data_In2...] all to just "pin".

- Delete original "exp" conduit.

6. Finish, save + overwrite edits, now "port edits" appear at the end of _hw.tcl file.

7. Copy "port edits" at end of _hw.tcl file.

8. Regenerate _hw.tcl file for DSPBuilder IP core using MATLAB play button.

9. Edit _hw.tcl using text editor, add "port edits" to end of _hw.tcl file, replacing "exp" conduit interface declaration.

10. Refresh Platform Designer using F5, add IP core to project. Now data signal conduits are properly configured for connecting to data signal conduits on MATLAB HDL Coder generated blocks, shown below.

Thank you to @sstrell for pointing out the easy/repeatable/bug-free way to edit conduit/data signal assignments from the Qsys component editor.

I borrowed this method to generate the _hw.tcl code necessary to define my custom port configuration.

Unfortunately in doing so, the rest of the _hw.tcl file was "wiped clean", but it is easy to regenerate in MATLAB.

I took the port configuration code generated from the component editor, and added it to my re-generated _hw.tcl file, and after refreshing Qsys, the ports on my DSPBA custom component are configured correctly.

Although slightly roundabout, this consistent UI-based procedure seems to work every time. Also, the port configuration _hw.tcl code generated from the component editor is re-usable as long as the DSPBA in/out data signals remain unchanged.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello, Ghe0rghe. I just wanted to advise that there might be a solution to your problem that might be more simple. Please see the KDB link below - involves checking the "use single conduit" button that is in the Control box in DSP Builder.

I am not 100% sure that this will solve your specific case, but worth looking at in case it saves you all of the modification steps.

Jeff

- Tags:

- DSPBA

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Glad to hear that you found the workaround. Please post a response in the next 15 days if you have further queries. After 15 days, this thread will be transitioned to community support. The community users will be able to help you with your follow-up questions.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page