- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

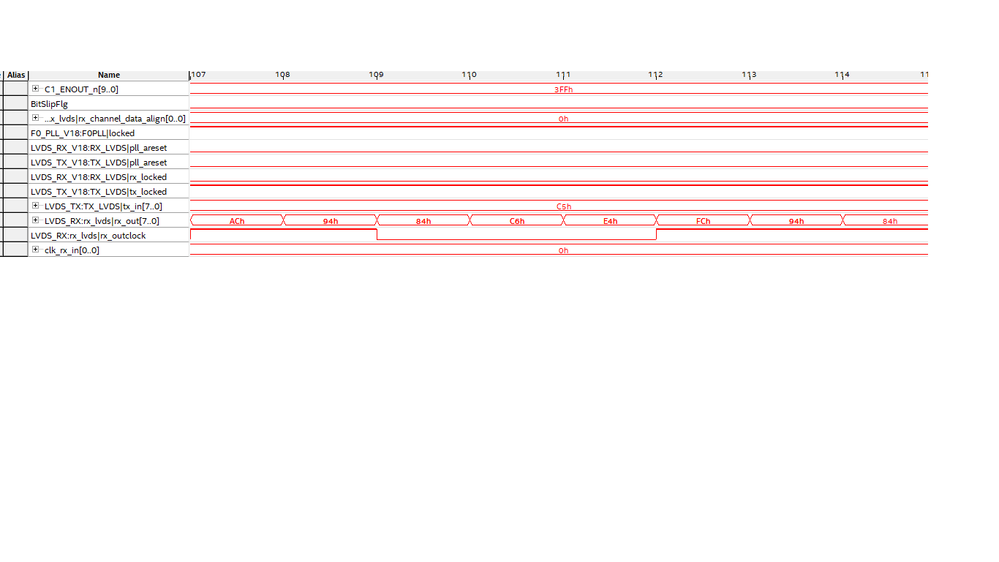

I am using ALTLVDS_RX IP on a Cyclone V GX device, and noticing that for some reason the rx_locked pin of PLL is never being locked. Same problem noticed is PLL is set to shared between transmitter and receiver.

I am new to ALTLVDS_RX. Can you please provide me some guidelines on what might be the issue. I am using a deserializer of 8, one channel and data rate 400Mbps and clock frequency 50MHz.

Attached are the timing diagram showing that rx_locked not being asserted.

링크가 복사됨

3 응답

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hi,

I am requesting to isolate the problem first, First make a simple LVDS Rx and requesting you to signal tap the signals. If still lock signal is not high, I am requesting to check the input to the clock ,is there any noise is been affected.

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Dear RSree,

Now I am having rx_clock and tx_clock pins are locked high now. I went to check with oscilloscope for the LVDS transmitter output clock tx_outclock but this is not being generated.

Why tx_outclock is not being generated?

Regards,

Clive

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hi,

There could be multiple reasons for not generating the clock may be the input will not be proper.

IP configuration will be proper or board level issues.