- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I've a question about the generation process of IP cores.

During my QSYS generation I'm always receiving bit width errors.

Furthermore in QSYS documentation there is a section which means the Avalon bit widths will be adapted with adapters.

During generation and IP creation there is no warning or error about bit width errors.

After generating everything I receive errors in synthesis.

I don't get it how autogenerated files can have any bit width issues?!

Do I have to adapt all files manually to make it running? I don't think this is the intention of the QSYS tool but if there are errors in autogenerated files it seems I have to do that...

Please see entity below and instantiation. Obviously there is an error in the bit width of the burst size.

entity avalon_ccb_read_pcie_controller is

generic (

DATA_WIDTH : integer := 256;

SYMBOL_WIDTH : integer := 8;

HDL_ADDR_WIDTH : integer := 32;

BURSTCOUNT_WIDTH : integer := 8;

COMMAND_FIFO_DEPTH : integer := 1024;

RESPONSE_FIFO_DEPTH : integer := 512;

MASTER_SYNC_DEPTH : integer := 2;

SLAVE_SYNC_DEPTH : integer := 2

);

component avalon_ccb_read_pcie_controller_cmp is

port (

m0_clk : in std_logic := 'X'; -- clk

m0_reset : in std_logic := 'X'; -- reset

s0_clk : in std_logic := 'X'; -- clk

s0_reset : in std_logic := 'X'; -- reset

s0_waitrequest : out std_logic; -- waitrequest

s0_readdata : out std_logic_vector(255 downto 0); -- readdata

s0_readdatavalid : out std_logic; -- readdatavalid

s0_burstcount : in std_logic_vector(6 downto 0) := (others => 'X'); -- burstcount

s0_writedata : in std_logic_vector(255 downto 0) := (others => 'X'); -- writedata

s0_address : in std_logic_vector(31 downto 0) := (others => 'X'); -- address

s0_write : in std_logic := 'X'; -- write

s0_read : in std_logic := 'X'; -- read

s0_byteenable : in std_logic_vector(31 downto 0) := (others => 'X'); -- byteenable

s0_debugaccess : in std_logic := 'X'; -- debugaccess

m0_waitrequest : in std_logic := 'X'; -- waitrequest

m0_readdata : in std_logic_vector(255 downto 0) := (others => 'X'); -- readdata

m0_readdatavalid : in std_logic := 'X'; -- readdatavalid

m0_burstcount : out std_logic_vector(6 downto 0); -- burstcount

m0_writedata : out std_logic_vector(255 downto 0); -- writedata

m0_address : out std_logic_vector(31 downto 0); -- address

m0_write : out std_logic; -- write

m0_read : out std_logic; -- read

m0_byteenable : out std_logic_vector(31 downto 0); -- byteenable

m0_debugaccess : out std_logic -- debugaccess

);

end component avalon_ccb_read_pcie_controller_cmp;

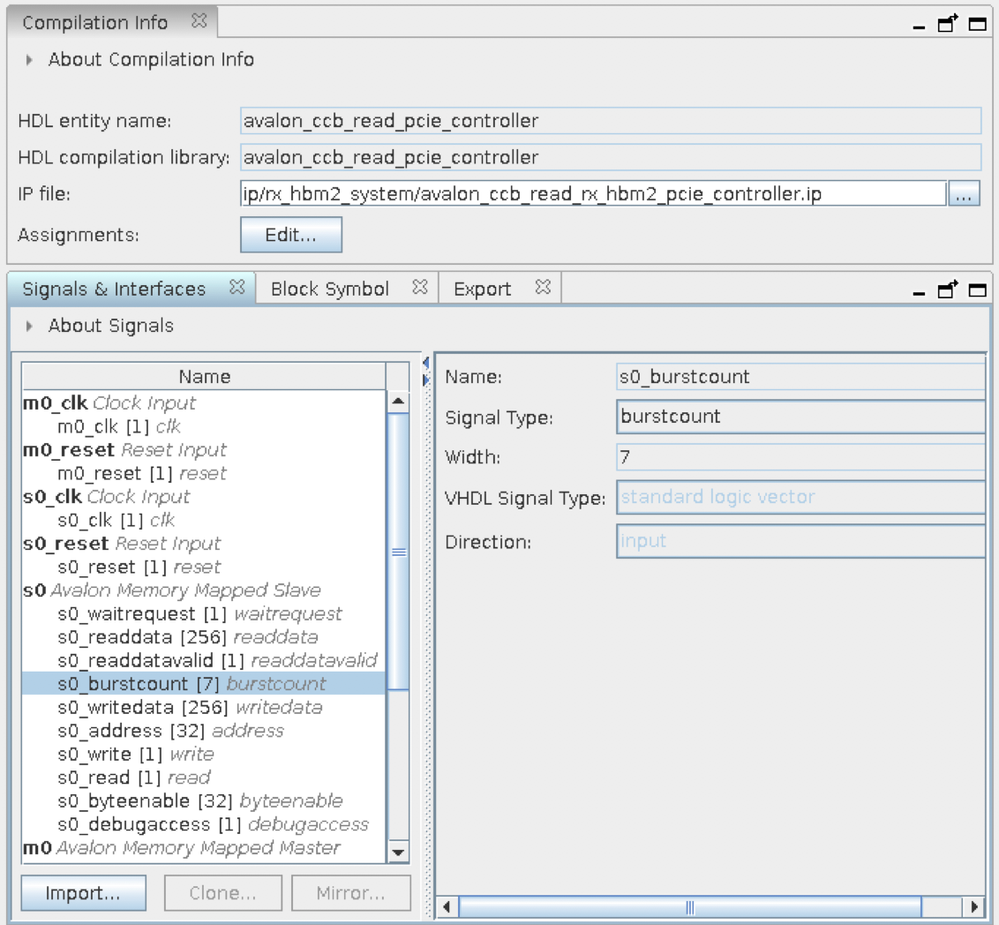

In QSYS the 7 bit is present but the generated top level has 8 bit:

I tried to clean the project, removed all generated files, generated several times and then synthesised but of course always the same error.

Best regards,

Michael

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

thanks for your reply.

i've recognised the .ip file is still the same after editing in QSYS (inside of my .qsys file).

I have fixed the bit width in the .ip file and now it's working!

Furthermore now the entity, Qsys and the instantiation has the bit width of 7 for the burst width.

Best regards,

Michael

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Theoretically, qsys should add in the adapter automatically. Can you attached the simple design for duplication of the issue?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The value of the generic doesn't necessarily have to match the actual hardware that's implemented. Are you saying that you specified 8 in the IP Parameter Editor, but you're only getting 7 bits for the burst count bus width?

#iwork4intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

thanks for your reply.

i've recognised the .ip file is still the same after editing in QSYS (inside of my .qsys file).

I have fixed the bit width in the .ip file and now it's working!

Furthermore now the entity, Qsys and the instantiation has the bit width of 7 for the burst width.

Best regards,

Michael

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Good to know that it is working, closing the thread. If you have further queries, Please post a response in the next 15 days

After 15 days, this thread will be transitioned to community support. The community users will be able to help you with your follow-up questions.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page